UNIVERSITA' DEGLI STUDI DI NAPOLI FEDERICO II Dottorato di Ricerca in Ingegneria Informatica ed Automatica

### A MODEL-DRIVEN METHODOLOGY FOR CRITICAL SYSTEMS ENGINEERING

FABIO SCIPPACERCOLA

Tesi di Dottorato di Ricerca (XXVIII Ciclo) MARZO 2016

Il Tutore

**Prof. Stefano Russo**

Il Coordinatore del Dottorato

**Prof. Francesco Garofalo**

Dipartimento di Ingegneria Elettrica e Tecnologie dell'Informazione

🖻 via Claudio, 21- I-80125 Napoli - 🖀 [#39] (0)81 768 3813 - 🏢 [#39] (0)81 768 3816

### A MODEL-DRIVEN METHODOLOGY FOR CRITICAL SYSTEMS ENGINEERING

By Fabio Scippacercola

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY AT "FEDERICO II" UNIVERSITY OF NAPLES VIA CLAUDIO 21, 80125 – NAPOLI, ITALY MARCH 2016

© Copyright by Fabio Scippacercola, 2016

# **Table of Contents**

| Ta            | ble o | of Cont    | tents                                               | iii  |

|---------------|-------|------------|-----------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Tables     | 3                                                   | vi   |

| $\mathbf{Li}$ | st of | Figure     | es                                                  | viii |

| A             | crony | <b>vms</b> |                                                     | xiii |

| A             | cknov | wledge     | ments                                               | xvii |

| In            | trod  | uction     |                                                     | 1    |

| 1             | Moo   | del-Dri    | iven Engineering                                    | 7    |

|               | 1.1   | Basic      | Concepts and Definitions                            | 7    |

|               |       | 1.1.1      | Model-Driven Architecture                           | 9    |

|               |       | 1.1.2      | MDA Viewpoints and Views                            | 14   |

|               |       | 1.1.3      | UML extensions of interest                          | 18   |

|               | 1.2   | State of   | of practice of MBE and MDE                          | 20   |

|               | 1.3   | Benefi     | ts and Open Challenges                              | 23   |

| <b>2</b>      | Lite  | rature     | Review                                              | 27   |

|               | 2.1   | Model      | -Driven Processes for Critical Systems              | 27   |

|               |       | 2.1.1      | Research questions                                  | 27   |

|               |       | 2.1.2      | Search process                                      | 28   |

|               |       | 2.1.3      | Inclusion and exclusion criteria                    | 28   |

|               |       | 2.1.4      | Paper classification                                | 29   |

|               |       | 2.1.5      | Data collection                                     | 29   |

|               | 2.2   | Search     | results                                             | 30   |

| 3             | ΑN    | lodel-l    | Driven Methodology for Critical Systems Engineering | 43   |

|               | 3.1   | Overvi     | iew                                                 | 43   |

|               | 3.2   | Roles a    | and Responsibilities                                | 48   |

|   | 3.3 | Model-Driven Development    49                                                                                                                                 |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.3.1 System Requirements Specification                                                                                                                        |

|   |     | 3.3.2 System Design 51                                                                                                                                         |

|   |     | 3.3.3 Component Design                                                                                                                                         |

|   |     | 3.3.4 Implementation $\ldots \ldots 54$               |

|   |     | 3.3.5 Early Fault Detection Techniques in Development                                                                                                          |

|   | 3.4 | Model-Driven Verification and Validation Design                                                                                                                |

|   |     | 3.4.1 Validation Design $\ldots \ldots \ldots$ |

|   |     | 3.4.2 Integration Verification Design                                                                                                                          |

|   |     | 3.4.3 Component Verification Design                                                                                                                            |

|   |     | 3.4.4 Early Fault Detection Techniques in V&V Design                                                                                                           |

|   | 3.5 | Model-Driven Verification and Validation Execution                                                                                                             |

|   |     | 3.5.1 Component Verification                                                                                                                                   |

|   |     | 3.5.2 Integration Verification                                                                                                                                 |

|   |     | 3.5.3 Validation $\ldots \ldots \ldots$        |

|   | 3.6 | Discussion                                                                                                                                                     |

| 4 | Mo  | del-Driven In-the-Loop Testing 71                                                                                                                              |

|   | 4.1 | Introduction                                                                                                                                                   |

|   | 4.2 | The Computational Independent Test Model                                                                                                                       |

|   | 4.3 | Discussion                                                                                                                                                     |

| 5 | Mo  | del-Driven Failure Mode and Effects Analysis 77                                                                                                                |

|   | 5.1 | Background                                                                                                                                                     |

|   | 5.2 | Overview of Model-Driven FMEA                                                                                                                                  |

|   | 5.3 | System Modeling                                                                                                                                                |

|   | 5.4 | FMEA Modeling                                                                                                                                                  |

|   |     | 5.4.1 FMEA Profile: the SysML FMEA Diagram                                                                                                                     |

|   |     | 5.4.2 MT2 transformation in Prolog 89                                                                                                                          |

|   | 5.5 | Model Analysis                                                                                                                                                 |

|   | 5.6 | An Eclipse-Based Support Tool                                                                                                                                  |

|   | 5.7 | Discussion                                                                                                                                                     |

| 6 | Cas | se study 1: Model-Driven Engineering of a Railway Interlocking Sys-                                                                                            |

|   | tem |                                                                                                                                                                |

|   | 6.1 | The Prolan Block Case Study                                                                                                                                    |

|   | 6.2 | Experimentation                                                                                                                                                |

|   |     | 6.2.1 System Requirements Specification                                                                                                                        |

|   |     | 6.2.2 System Design                                                                                                                                            |

|   |     | 6.2.3 Component Design                                                                                                                                         |

|   |     | $6.2.4$ Implementation $\ldots \ldots \ldots$  |

|              |     | 6.2.5           | Validation Design                                       | 116                                      |

|--------------|-----|-----------------|---------------------------------------------------------|------------------------------------------|

|              |     | 6.2.6           | Integration Verification Design                         | 116                                      |

|              |     | 6.2.7           | Component Verification Design                           | 121                                      |

|              |     | 6.2.8           | Model-Driven V&V Subprocess                             | 122                                      |

|              | 6.3 | Discus          | ssion                                                   | 123                                      |

| 7            | Cas | e stud          | y 2: Model-Driven In-the-Loop Testing in Railway Domain | 127                                      |

|              | 7.1 | The P           | Prolan Monitor Case Study                               | 127                                      |

|              | 7.2 | Exper           | imentation                                              | 128                                      |

|              |     | 7.2.1           | Model-driven development                                | 128                                      |

|              |     | 7.2.2           | The Computational Independent Test Model                | 133                                      |

|              |     | 7.2.3           | Model-in-the-loop testing                               | 138                                      |

|              |     | 7.2.4           | Software- and Hardware-in-the-loop testing              | 141                                      |

|              | 7.3 | Discus          | ssion                                                   | 143                                      |

| 8            | Cas | e stud          | y 3: Model-Driven FMEA in Automotive Domain             | 145                                      |

|              | 8.1 |                 | imentation                                              | 145                                      |

|              |     | 8.1.1           | System Modeling                                         | 146                                      |

|              |     | 8.1.2           | FMEA Modeling                                           | 151                                      |

|              |     | 8.1.3           | M2T trasformation                                       | 153                                      |

|              |     | 0.1.0           |                                                         | 100                                      |

|              |     | 8.1.4           | Model Analysis                                          | 155                                      |

|              | 8.2 | 8.1.4           |                                                         |                                          |

| $\mathbf{C}$ | 0   | 8.1.4           | Model Analysis                                          | 155                                      |

| $\mathbf{C}$ | 0   | 8.1.4<br>Discus | Model Analysis                                          | $\begin{array}{c} 155\\ 162 \end{array}$ |

|              | 0   | 8.1.4<br>Discus | Model Analysis                                          | $\begin{array}{c} 155\\ 162 \end{array}$ |

# List of Tables

| Common OMG standards in MDA                         | 14                          |

|-----------------------------------------------------|-----------------------------|

| An example on the MDA views                         | 16                          |

| The typologies adopted for classifying the studies. | 31                          |

| Typologies of papers by Industry Domain             | 34                          |

| Differences between the frameworks SXF and OXF      | 114                         |

|                                                     |                             |

| CPT test categories.                                | 139                         |

| CPT test categories                                 |                             |

| -                                                   | 139                         |

| Specification of the MIL test cases                 | 139                         |

|                                                     | An example on the MDA views |

# List of Figures

| 1.1 | The terminology adopted in the thesis                                              | 8  |

|-----|------------------------------------------------------------------------------------|----|

| 1.2 | Document-centric and Model-centric approaches                                      | 8  |

| 1.3 | The OMG Modeling infrastructure                                                    | 12 |

| 1.4 | Services and computing environments defined by the MDA $\ldots \ldots \ldots$      | 13 |

| 1.5 | The MDA Viewpoints.                                                                | 17 |

| 1.6 | The overlap between UML and SysML                                                  | 19 |

| 1.7 | The integration of MDA and MDT proposed by Dai [17].                               | 20 |

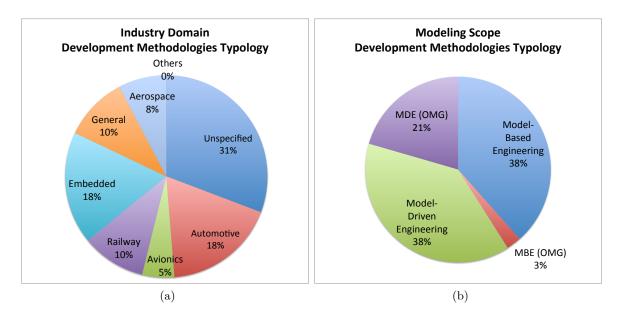

| 2.1 | Distribution of reviewed papers by Typology and Industry Domain                    | 32 |

| 2.2 | Distribution of all reviewed studies by Industry Domain and Modeling Scope         | 34 |

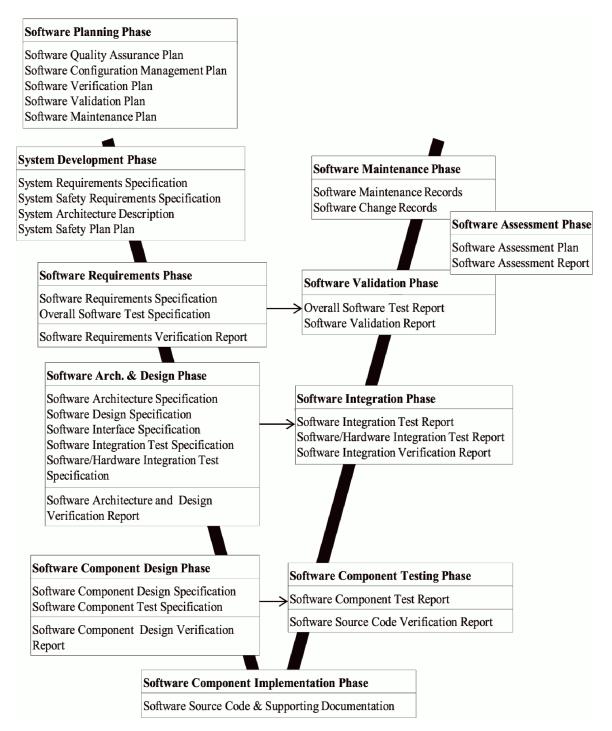

| 3.1 | EN 50128 Software Development Life cycle                                           | 44 |

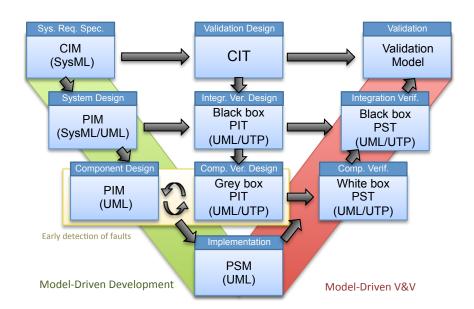

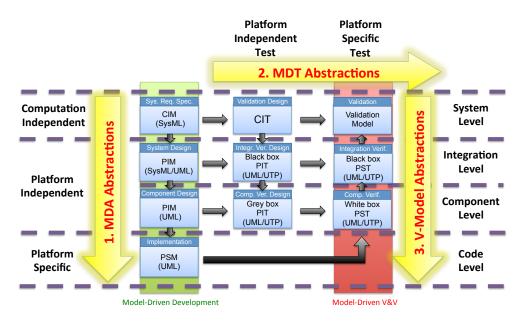

| 3.2 | The proposed model-driven V-Model life cycle                                       | 46 |

| 3.3 | The three main abstractions exploited in the model-driven life cycle $\ . \ . \ .$ | 46 |

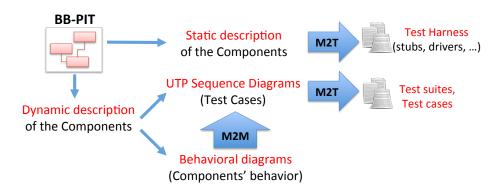

| 3.4 | The transformations of the BB-PIT.                                                 | 58 |

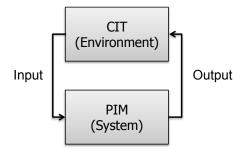

| 4.1 | The CIT and the PIM in configuration <i>in-the-loop</i>                            | 72 |

| 4.2 | Back-to-back testing                                                               | 75 |

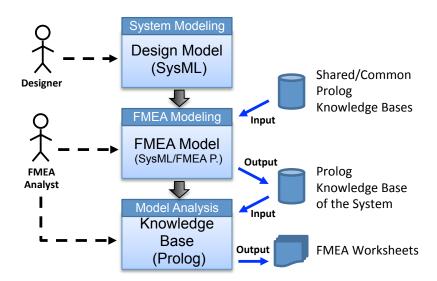

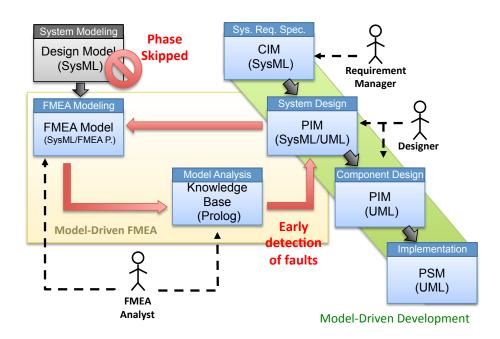

| 5.1 | Overview of the proposed model-driven FMEA process                                 | 81 |

| 5.2 | Integration of the FMEA approach in the proposed life cycle $\ldots$               | 82 |

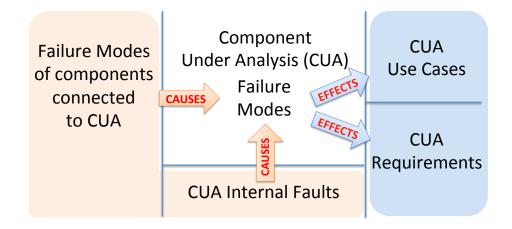

| 5.3 | Logical layout of a FMEA diagram                                                   | 87 |

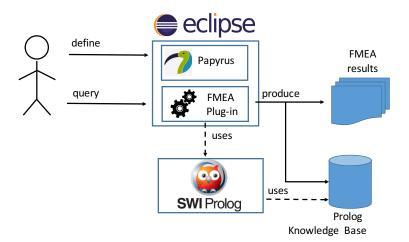

| 5.4 | An Eclipse-based architecture for model-driven FMEA approach                       | 92 |

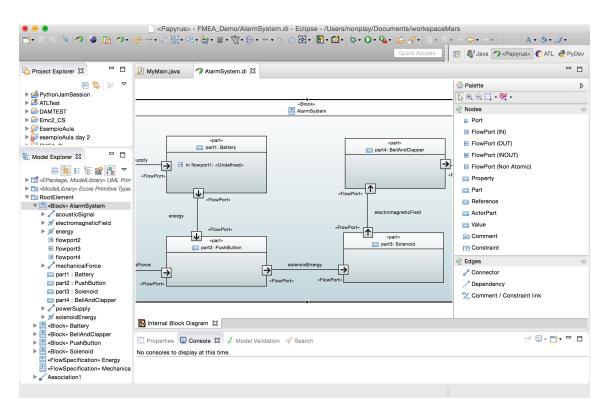

| 5.5 | SysML modeling with Papyrus                                                        | 93 |

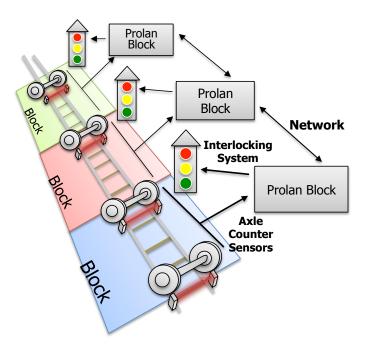

| 6.1 | A representation of the Prolan Block                                               | 98 |

|     |                                                                                    |    |

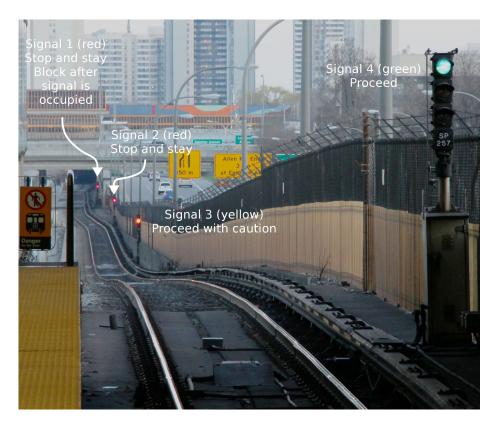

| 6.2  | Short railway blocks on the Toronto subway                                                         | 99  |

|------|----------------------------------------------------------------------------------------------------|-----|

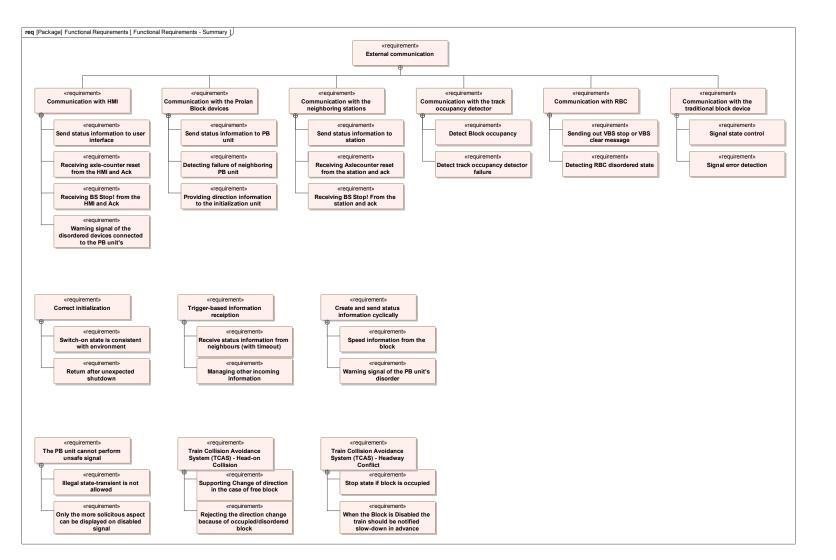

| 6.3  | CIM SysML Requirement Diagram showing system functional requirements.                              | 102 |

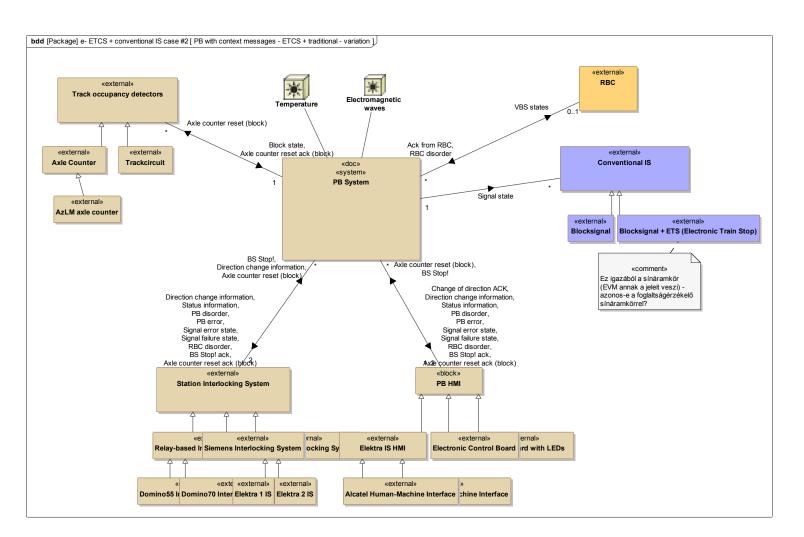

| 6.4  | CIM SysML BDD showing the PB within its environment                                                | 103 |

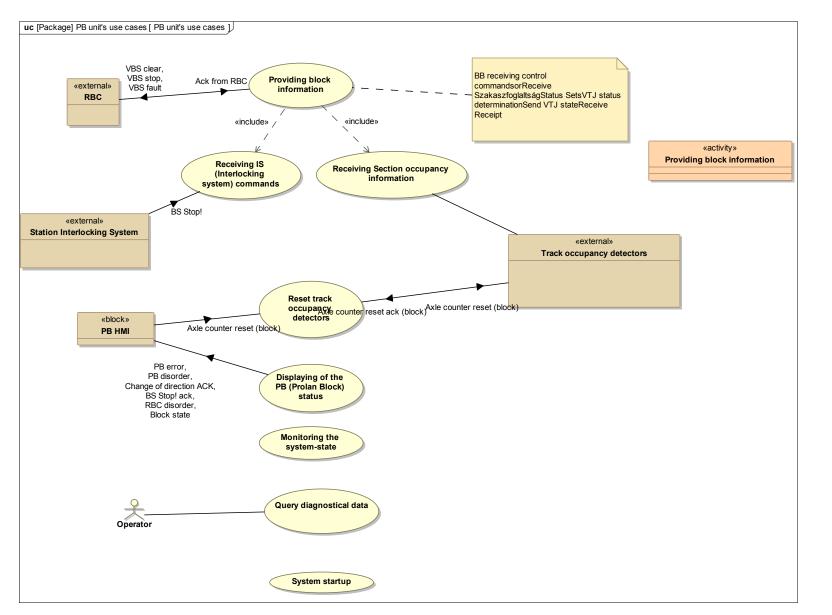

| 6.5  | CIM Use Case Diagram for the Prolan Block.                                                         | 104 |

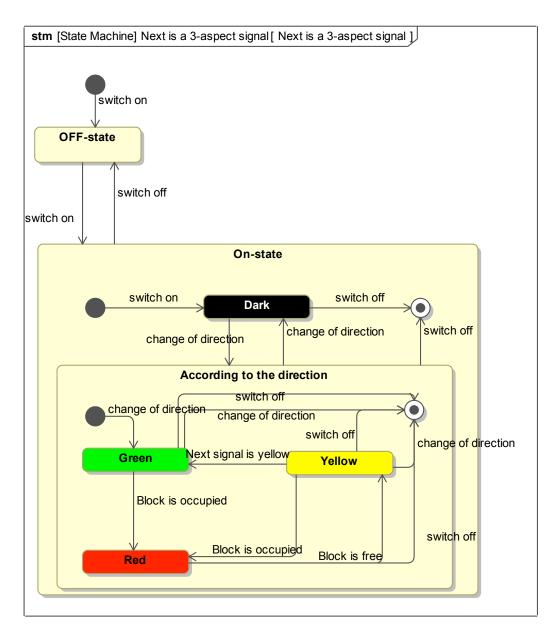

| 6.6  | CIM SysML State Machine Diagram specifying the semaphore's behavior                                | 105 |

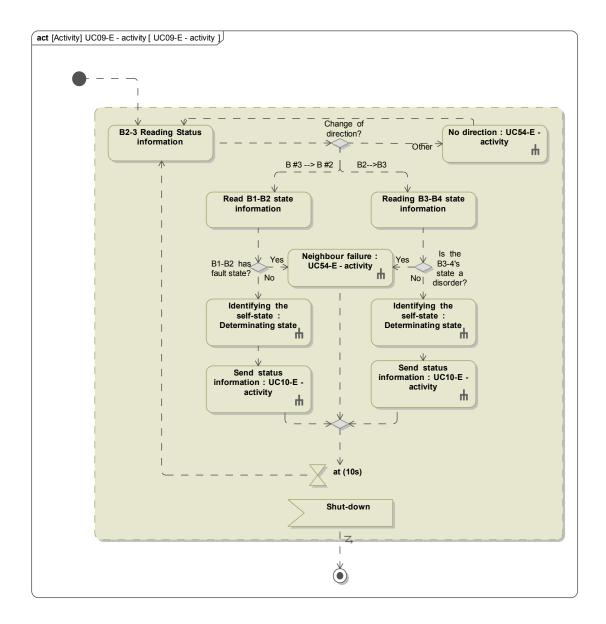

| 6.7  | CIM SysML Activity Diagram specifying the use case Processing Status In-                           |     |

|      | formation                                                                                          | 106 |

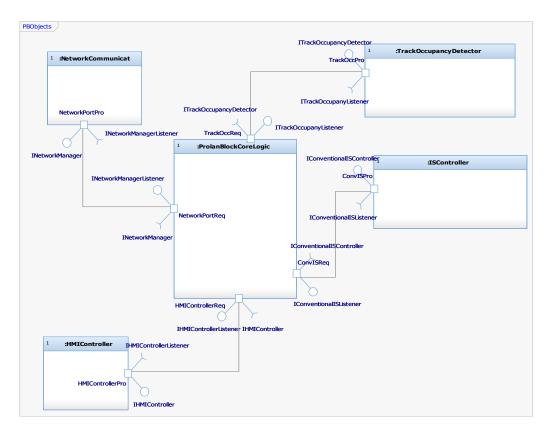

| 6.8  | High-level system architecture.                                                                    | 108 |

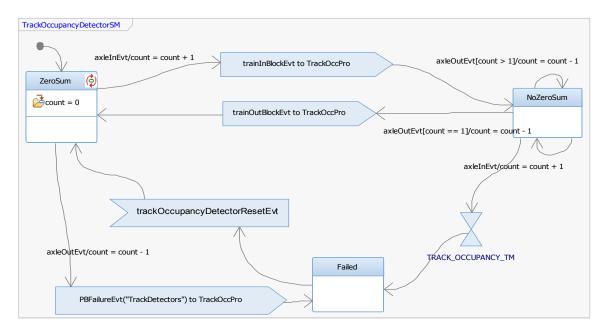

| 6.9  | The PIM state diagram of the behavior of the $\mathit{TrackOccupancyDetector.}$                    | 110 |

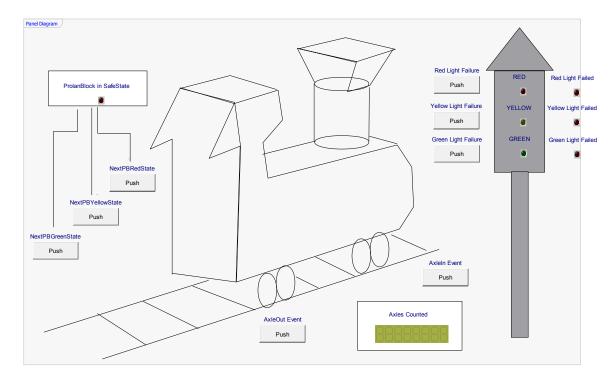

| 6.10 | The IBM Rhapsody <sup>©</sup> Panel diagram for the Prolan Block. $\ldots$                         | 111 |

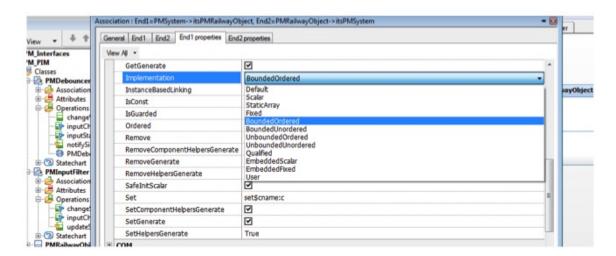

| 6.11 | Specification of platform specific properties in IBM Rhapsody $^{\odot}$                           | 113 |

| 6.12 | Fragment of the code automatically generated                                                       | 115 |

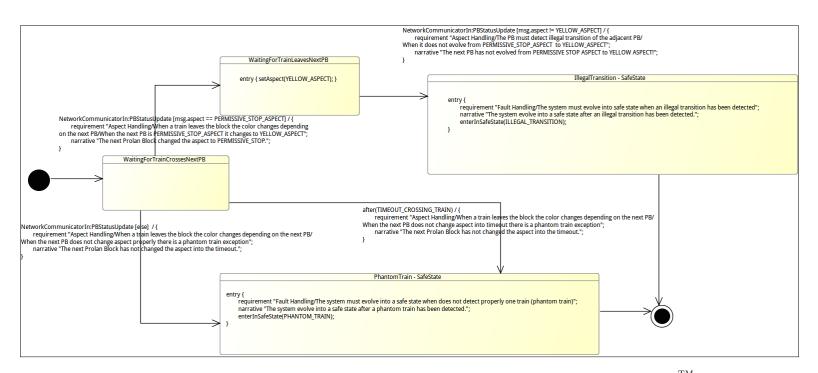

| 6.13 | A BB-PIT QML State Machine used for test case generation in $Conformiq^{TM}$ .                     | 119 |

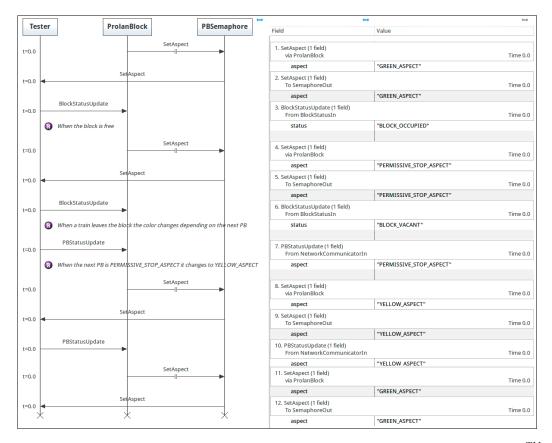

| 6.14 | A test case automatically generated from the BB-PIT by $\operatorname{Conformiq}^{^{\mathrm{TM}}}$ | 120 |

| 6.15 | The Traceability Matrix automatically generated by $Conformiq^{TM}$                                | 120 |

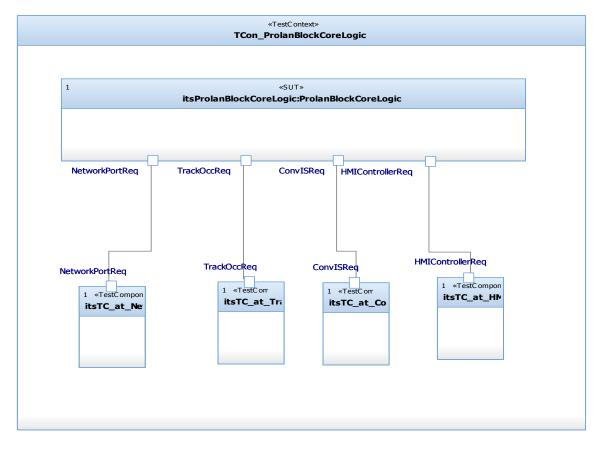

| 6.16 | The testing harness automatically generated by TestConductor for the Prolan-                       |     |

|      | BlockCoreLogic.                                                                                    | 121 |

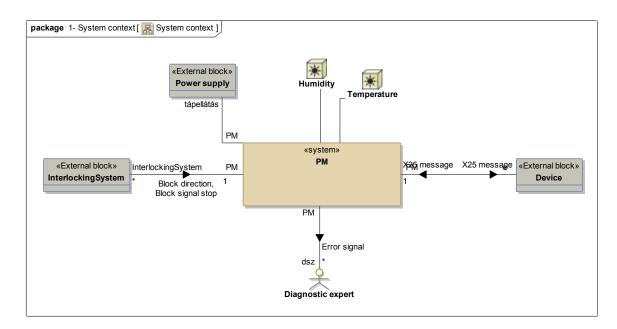

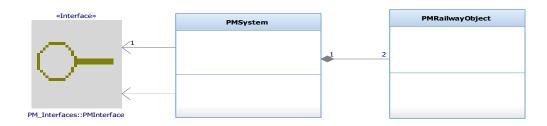

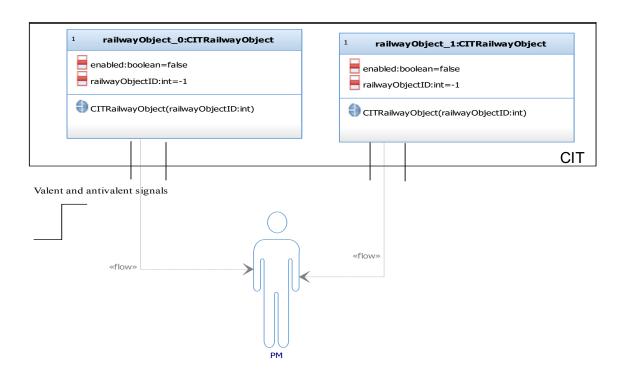

| 7.1  | SysML Block Definition Diagram of the CIM of the PM                                                | 129 |

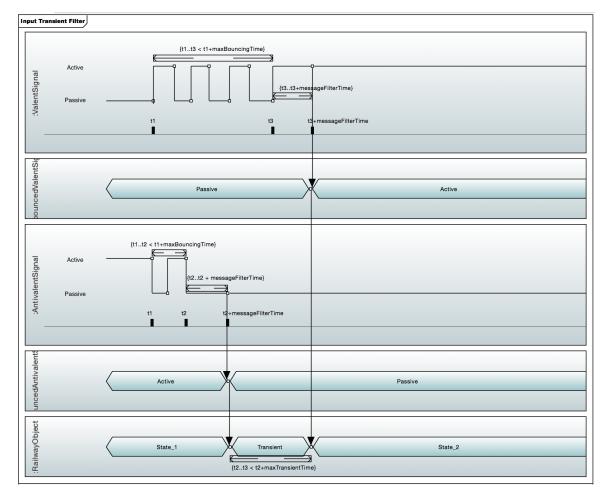

| 7.2  | A UML Timing Diagram included in the CIM, representing the requirements                            |     |

|      | for the functionality of signal debouncing.                                                        | 130 |

| 7.3  | High level architecture of the Prolan Monitor                                                      | 131 |

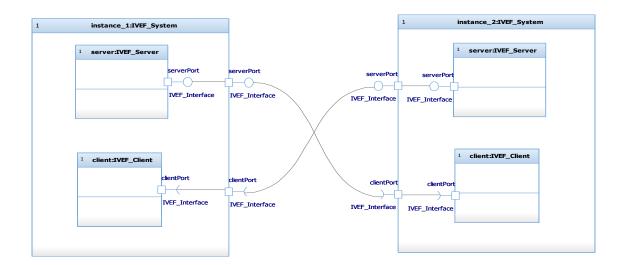

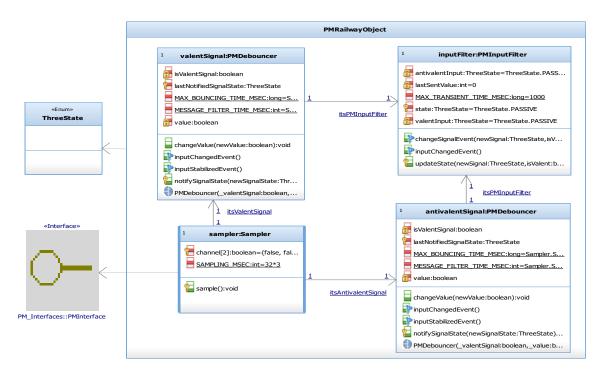

| 7.4  | UML Internal Structure Diagram of the <i>PMRailwayObject</i>                                       | 131 |

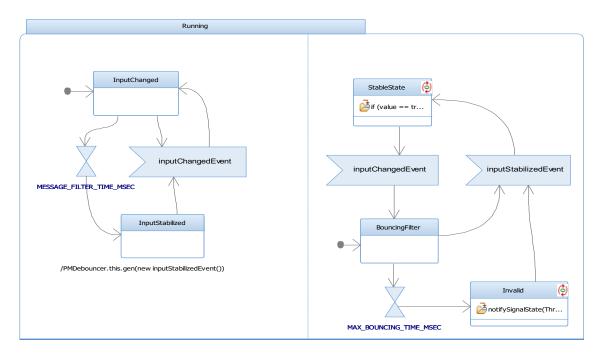

| 7.5  | UML Behavioral State Machine of the <i>PMDebouncer</i>                                             | 132 |

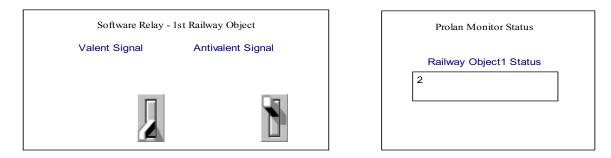

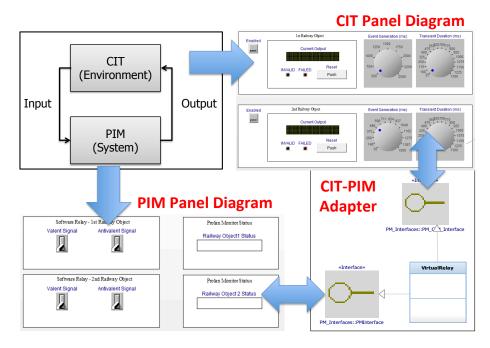

| 7.6  | Rhapsody Panel Diagram associated to the PIM                                                       | 133 |

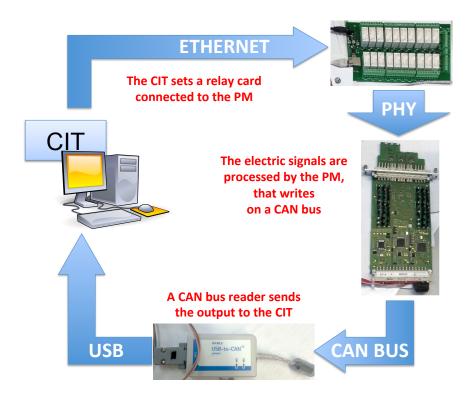

| 7.7  | The architecture of the CIT.                                                                       | 134 |

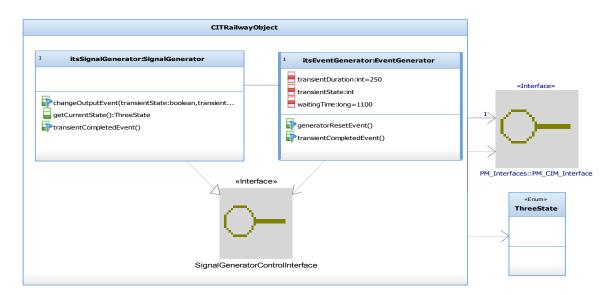

| 7.8  | The internal design of the CITRailwayObject                                                        | 134 |

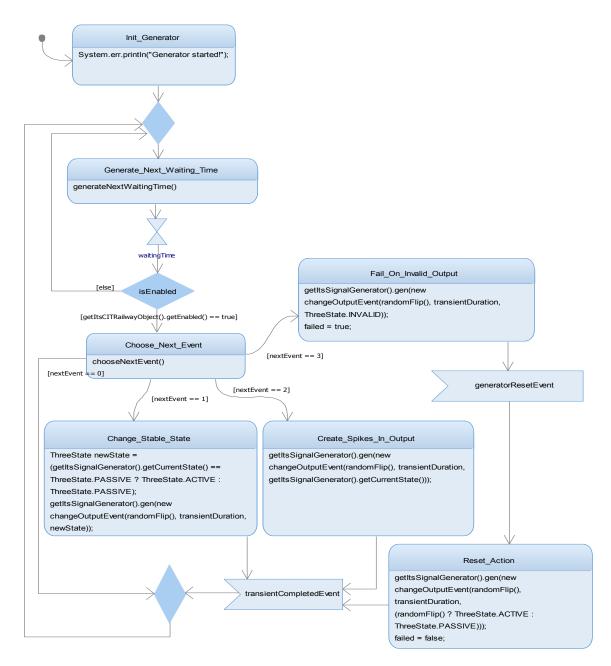

| 7.9  | UML Activity diagram of the <i>EventGenerator</i>                                                  | 136 |

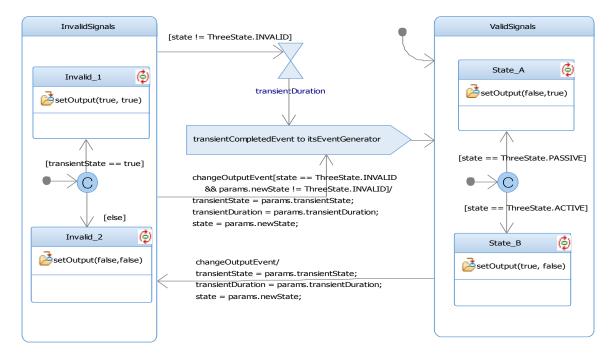

| 7.10 | UML Behavioral State Machine model of the SignalGenerator                                          | 137 |

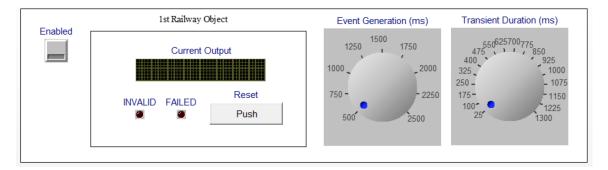

| 7.11 | Rhapsody Panel Diagram of the CITRailwayObject.                                                    | 137 |

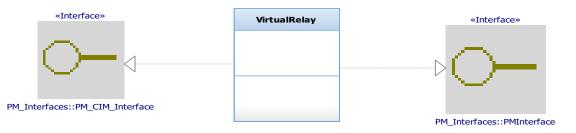

| 7.12 | The CIT-PIM software adapter                                                                       | 138 |

| 7.13 | The configuration of the PM for MIL Testing                                                        | 140 |

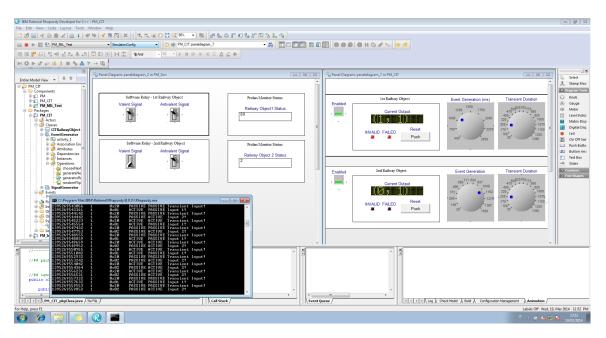

| 7.14 | Screenshot of the MIL testing                                                  |     |  |  |

|------|--------------------------------------------------------------------------------|-----|--|--|

| 7.15 | The configuration of the PM for HIL Testing.                                   |     |  |  |

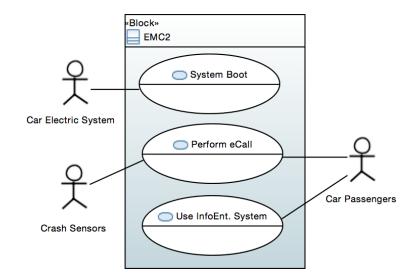

| 8.1  | Excerpt of Use Cases Diagram of $\text{EMC}^2$ prototype                       | 147 |  |  |

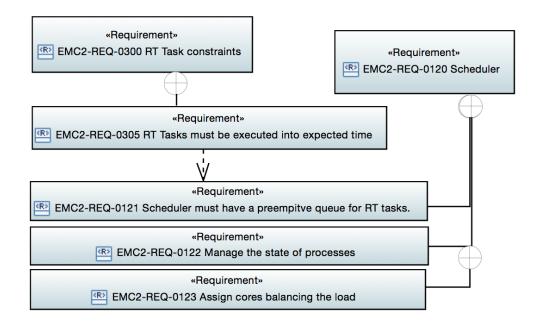

| 8.2  | Excerpt of SysML Requirements Diagram of $EMC^2$                               |     |  |  |

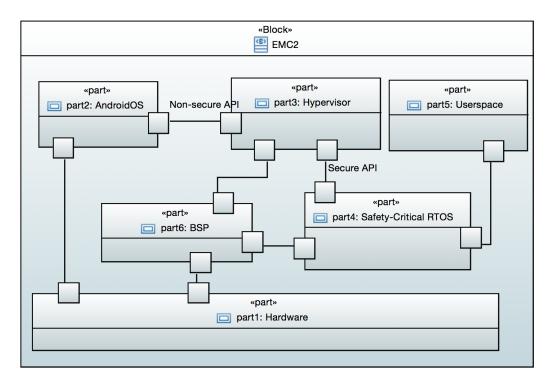

| 8.3  | SysML Internal Block Diagram of the $\text{EMC}^2$ prototype                   |     |  |  |

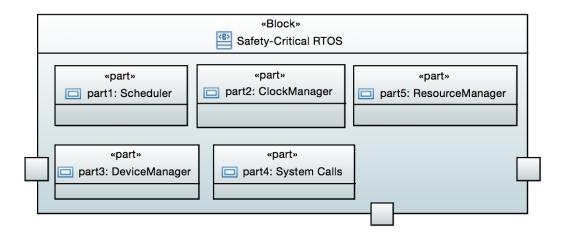

| 8.4  | Internal Block Diagram of the Safety-Critical RTOS Component 14                |     |  |  |

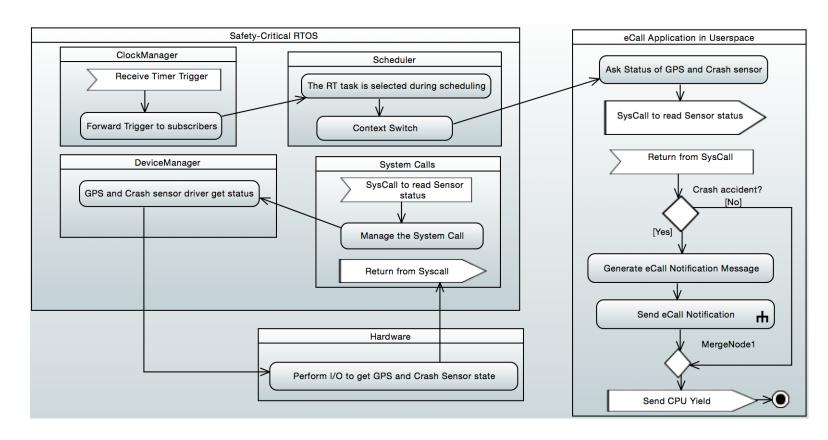

| 8.5  | Activity Diagram of the use case Perform eCall                                 | 150 |  |  |

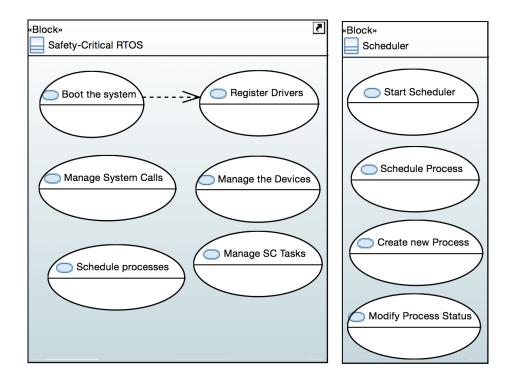

| 8.6  | Use Cases for the SC-RTOS and Scheduler components                             | 151 |  |  |

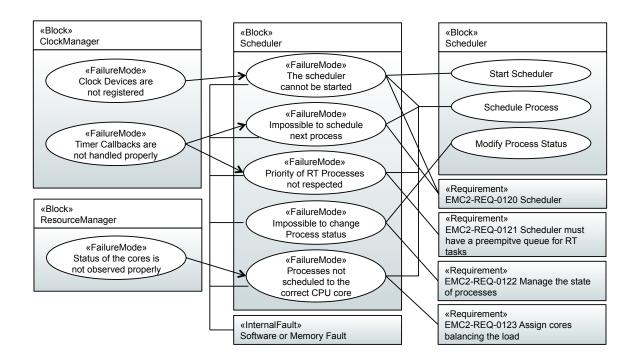

| 8.7  | FMEA Diagram for the EMC <sup>2</sup> Scheduler component                      | 153 |  |  |

| 8.8  | Fragment of the Prolog Knowledge Base relative to the <i>Scheduler</i> 15      |     |  |  |

| 8.9  | 8.9 Fragment of the Prolog shared Knowledge Base defining predicates for model |     |  |  |

|      | analysis.                                                                      | 157 |  |  |

| 8.10 | Results of the execution of the query 1 on the $EMC^2$ knowledge base          | 158 |  |  |

| 8.11 | Results of the execution of the query 2 on the $EMC^2$ knowledge base          | 159 |  |  |

| 8.12 | Results of the execution of the query 3 on the $EMC^2$ knowledge base          | 160 |  |  |

### Acronyms

**ALF** OMG Action Language for UML.

**BB-PIT** Black Box Platform Independent Test Model, Sec. 3.4.2.

**BB-PST** Black Box Platform Specific Test Model, Sec. 3.5.2.

**BDD** SysML Block Definition Diagram.

**BSP** Board Support Package, Sec. 8.1.1.

**CAN** Controller Area Network (Bus).

CIM Computation Independent Model, Sec. 1.1.2.

- CIT Computation Independent Test Model, Sec. 3.4.1.

- CIV Computation Independent Viewpoint, Sec. 1.1.2.

- **CPT** Category Partition Testing.

- CUA Component Under Analysis, Sec. 5.4.1.

- **DSL** Domain-Specific Language.

ETCS European Train Control System, Sec. 6.2.1.

- FMEA Failure Mode and Effects Analysis, Sec. 5.1.

- **fUML** OMG Semantics of a Foundational Subset for Executable UML Models.

- **GB-PIT** Grey Box Platform Independent Test Model, Sec. 3.4.3.

- HIL Hardware-in-the-loop.

- HMI Human-Machine Interface, Sec. 6.2.1.

- **IBD** SysML Internal Block Diagram.

- **IS** Interlocking System, Sec. 6.2.1.

xiv

- **KB** Knowledge Base.

- M2M Model-to-Model Transformation, Sec. 1.1.

- M2T Model-to-Text Transformation, Sec. 1.1.

- **MBE** Model-Based Engineering, Sec. 1.1.

- MDA Model-Driven Architecture, Sec. 1.1.

- MDD Model-Driven Development, Sec. 1.1.

- MDE Model-Driven Engineering, Sec. 1.1.

- **MDT** Model-Driven Testing, Sec. 1.1.

- **MIL** Model-in-the-loop.

- **OMG** Object Management Group.

- **OS** Operating System.

- **OXF** IBM Rhapsody Object Execution Framework, Sec. 6.2.4.

- **PB** Prolan Block, Sec. 6.1.

- **PIM** Platform Independent Model, Sec. 1.1.2.

- **PIT** Platform Independent Test Model, Sec. 1.1.3.

- **PIV** Platform Independent Viewpoint, Sec. 1.1.2.

- **PM** Prolan Monitor, Sec. 7.1.

- **PSM** Platform Specific Model, Sec. 1.1.2.

- **PST** Platform Specific Test Model, Sec. 1.1.3.

- **PSV** Platform Specific Viewpoint, Sec. 1.1.2.

- **RAMS** Reliability, Availability, Maintainability and Safety.

- **RBC** Radio Block Centre, Sec. 6.2.1.

- **RTOS** Real-Time Operating System.

- **SDLC** Software Development Life Cycle.

- SEEA Software Error Effect Analysis, Sec. 5.2.

- **SIL** Safety Integrity Level.

- ${\bf SPLC}\,$  Software Product Life Cycle.

- ${\bf SUT}$  System Under Test.

- **SXF** IBM Rhapsody Simple Execution Framework, Sec. 6.2.4.

- SysML OMG Systems Modeling Language, Sec. 1.1.3.

- **UML** OMG Unified Modeling Language.

- **UTP** UML Testing Profile, Sec. 1.1.3.

- $\mathbf{V}\&\mathbf{V}$  Verification and Validation.

- **WB-PST** White Box Platform Specific Test Model, Sec. 3.5.1.

## Acknowledgements

I believe that from the eyes of other people I could have given the impression to be a person selfish of words or feelings in the past. But the truth is that I extremely care of who I am fond of, so much that sometimes I was scared about how my words and actions would have been interpreted by them.

A Ph.D. teaches you to expose your opinions, thought and theses. And not only these; I skipped the acknowledgements in my BSc and MSc dissertations, now it is time to move on.

I would like to deeply thank all who have been around me in this academic path: my supervisor, prof. Stefano Russo, and all professors, researchers and colleagues (but I would like to call them friends) of the MOBILAB and CINI. I cannot forget to mention, András Zentai, Nuno Silva, my family, and all my best friends.

Thanks by heart.

Napoli, Italy March 31, 2016 Fabio

## Introduction

Software engineering, as most of branches of engineering, has always evolved increasing the level of abstractions. If we just look at one of the most peculiar and fascinating technology of this discipline, the programming languages, we will note how the first abstractions, i.e., the second generation languages – the *assembly languages* –, were born soon after programmers had struggled with machine codes; then came the third generation programming languages, that freed the programmers from low level details of the machine, and finally the fourth generation languages, which added more facilities and masked recurrent problems, such as the representation of data and the interworking between heterogeneous systems. In this perspective, Model-Driven Engineering (MDE) aims at raising the level of abstraction in software design and verification [1], and promises to innovate the traditional methodologies of software development.

Model-driven approaches focus on a *model*, i.e., on descriptions of a system that neglect aspects that are not of interest at the current stage in a software process; the process advances transforming the model in documents, intermediate artifacts, or in the final product. The result is that MDE is going to shift the traditional development paradigm, based on different kinds of artifacts composed by domain experts in multiple formats, to a common formalism – the model –, by which the artifacts are obtained through computer-assisted transformations. This *model-centric* paradigm introduces several benefits into the process, and leads to better productivity and quality of artifacts, shorter development time, and enhanced automation, which includes automatic code generation and support to the activities of verification and validation.

Due to these benefits, industry is increasing the adoption of MDE. This is shown by recent industrial surveys, which investigated the adoption of MDE methodologies and technologies in practice [2, 3]. In particular, MDE is attractive for the development of critical systems, since it can speed up the activities of Verification and Validation (V&V): model-driven approaches are widely exploited in industry for the early verification of the systems, through techniques such as model reviews, guideline checkers, Rapid Control Prototyping and Model- and Software- in-the-loop Tests. These techniques shift the cost of development from the phases of V&V to the ones of requirement analysis and design, but lead to benefits in terms of residual errors. Companies not performing model-in-the-loop testing find almost 30% more errors during module test [4].

Incorporating model-driven techniques into a legacy well-proven development processes is not simply a matter of placing models and transformations in traditional methodologies: the activities have to be carefully redesigned to exploit the benefits of MDE, and the skills and expertise of the engineers. Indeed, success stories on the adoption of MDE are reported after long time of technological innovation, that required several pilot project experiments, and the rethinking of traditional activities, complemented by custom supporting tools. Motorola could achieve an increase of quality and productivity (ranging from 1.2x to 8x), and an approximately 33% reduction in the effort required to develop test cases, after 15 years of wide spectrum adoption of MDE [5, 6]; the recent case study in [7] reports the successful introduction of a MBE process after four years and three projects had been defined and consolidated.

The problem of defining a model-driven life cycle is exacerbated in critical domains, where the process has to comply to strict requirements to assure high level of quality of the artifacts. In fact, in safety-critical domain, the efforts for verification and validation account for the major part of the costs, while safety standards require accurate assessments of the system and prescribe qualified tools.

Past studies attempted to apply pre-existing processes to MDE, or to create new ones [8], but these approaches cannot be proposed as a replacement of current industrial practices, especially for the development of certified critical systems. There are still few model-driven methodologies that cover the full system development life cycle, and that are suited to apply MDE on a large scale, in processes shared among more partners.

Indeed, few previous approaches targeted to offer flexible and complete model-driven life cycles that could be customized for industrial needs, and, in particular, designed for critical domains, where is the demand to support a broad range of activities of V&V and comply with standards and open technologies.

The need of a consolidated MDE methodology was also experienced personally by the Ph.D. candidate, during twelve-months of industrial-academic partnership in which he was involved: in the framework of the European project "CErtification of CRItical Systems" (CECRIS, [9]), the candidate participated to a transfer of knowledge of MDE technologies in Prolan Co., a Hungarian company which develops certified products for safety critical process control and rail signalling systems; during this activity, it emerged the lack of well-defined processes for the development of a CENELEC SIL-4 safety critical signalling system that was suited for the real industrial needs.

#### Thesis contribution

- 1. This thesis proposes a novel model-driven life cycle that is tailored to the development of critical systems, and overcomes limitations of previous approaches:

- It covers the full software life cycle and is suited to replace current industrial processes, in particular for the development of products that undergo to CENELEC 50128 certification;

- It supports several techniques of Verification and Validation in a conventional V-Model, including techniques of early fault detection, and safety assessment;

- It benefits from OMG standards, adopting Model-Driven Architecture (MDA), SysML, UML and Model-Driven Testing (MDT).

- 2. The methodology integrates an original approach for model-driven system validation, based on a new model named *Computation Independent Test model* (CIT), that is exploited to perform *Model-, Software-, and Hardware- In-the-loop testing.*

- 3. Moreover, the process supports the Failure Modes and Effect Analysis (FMEA), with a novel approach to conduct Model-Driven FMEA, based on custom SysML Diagram, namely the *FMEA Diagram*, and Prolog.

Since the thesis benefits from the fruitful collaboration with industry, **the approaches have been experimented in multiple real-world case studies, from railway and automative domains**, offered by the industrial partners. Two case studies of CENELEC 50128 SIL-4 signalling systems have been provided by Prolan, whereas one automotive case study has been provided by the Portuguese company Critical Software SA, that develops safety-critical systems and provides consulting and expertise for the certification.

Finally, as an additional contribution of this thesis, the author aims at increasing the knowledge on MDE success and failure factors, since more concrete industrial experiences are necessary to get a clear comprehension of risks and benefits of MDE, especially for critical systems [8].

The work includes material from the following research papers, already accepted or published in peer-reviewed conferences:

F. Scippacercola, R. Pietrantuono, S. Russo, A. Zentai, "Model-Driven Engineering of a Railway Interlocking System", In: Proc. of the 3rd International Conference on Model-Driven Engineering and Software Development (MODELSWARD 2015). 2015, pp. 509-519. SCITEPRESS. ISBN: 978-989-758-083-3.

- F. Scippacercola, R. Pietrantuono, S. Russo, A. Zentai, "Model-in-the-loop Testing of a Railway Interlocking System", In: *Model-Driven Engineering and Software Development*. 2015, Communications in Computer and Information Science (CCIS), vol. 580, pp. 375-389, Springer International Publishing. DOI: 10.1007/978-3-319-27869-8; ISSN: 1865-0929; ISBN: 978-3-319-27868-1.

- F. Scippacercola, R. Pietrantuono, S. Russo, N. P. Silva, "SysML-based and Prolog-supported FMEA", In: Proc. of the 2015 IEEE International Symposium on Software Reliability Engineering Workshops (ISSREW). 2015, pp. 174-181, IEEE. ISBN: 978-1-5090-0406-5.

- F. Scippacercola, R. Pietrantuono, S. Russo, A. Esper, N. Silva, "Integrating FMEA in a Model-Driven Methodology", accepted to the International Space Sysem Engineering Conference (DASIA). 2016.

The first study presents the proposed model-driven development life cycle (thesis contribution 1), the second one focuses on the CIT and on the Model-in-the-loop extension (thesis contribution 2), while the third and forth scientific papers introduce the modeldriven FMEA and FMEA Diagram (thesis contribution 3).

The dissertation is organized as follows:

**Chapter 1** introduces the main concepts of Model-Driven Engineering and Model-Driven Architecture, then presents a discussion on the current state of practice of model-based and model-driven approaches.

Chapter 2 presents a systematic literature review on model-driven processes for critical systems, and discusses the limitations of previous studies.

**Chapter 3** introduces the novel model-driven methodology for critical systems engineering, and discusses its benefits.

**Chapter 4** presents details the Computation Independent Test Model, and the benefits from environmental modeling in the software development life cycle.

**Chapter 5** presents our proposal for a model-driven Failure Mode and Effects Analysis, and the novel SysML FMEA Diagram.

**Chapter 6** introduces our experience with the proposed development life cycle on a case study on the Prolan Block, a safety-critical part of an interlocking system provided by

Prolan.

**Chapter 7** presents the Prolan Monitor, another safety-critical system provided by Prolan, and the experience with the CIT and in-the-loop testing.

**Chapter 8** discusses an automotive safety-critical system provided by Critical Software, on which we performed a FMEA using the proposed approach.

### Chapter 1

## **Model-Driven Engineering**

#### **1.1** Basic Concepts and Definitions

Since models have always been applied at different extents in many problems and activities, there are many acronyms with fuzzy borders in the universe of software engineering. In this thesis we refers to the terminology of [10].

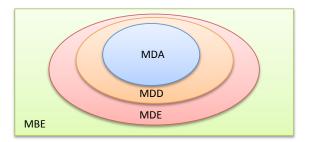

When processes exploit models as support for their goals they are part of *Model-Based Engineering* (MBE), and we call the activities *document-centric*, since models are only a means to achieve the targets, but there is not particular emphasis on them. Therefore MBE is the broadest term that cover all the methodologies and activities that employ models (Fig. 1.1).

*Model-Driven Engineering* (MDE) focuses on the processes where models are key artifacts of the activities (*model-centric*). When we restrict to considering MDE for supporting the development of systems, we can use the more specific term of *Model-Driven Development* (MDD). One approach of MDD is the *Model-Driven Architecture* (MDA), proposed by the Object Management Group (OMG) [11]. The *Model-Driven Testing* (MDT) is a theory of software testing that introduces concepts enabling to transform models in test-cases in order to support verification and validation activities. Even though MDT is not an OMG standard, it uses an OMG's standard profile, the *UML Testing Profile* (UTP).

Figure 1.1: The terminology adopted in the thesis.

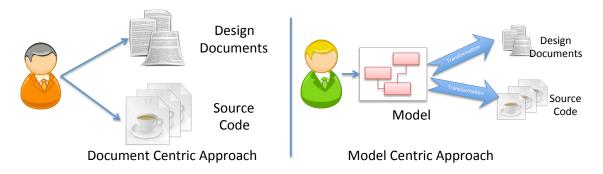

MDE is founded on concepts of *models* and *transformations*: instead of producing (textual) documents as artifacts – requirements, design, code, test artifacts – engineers, in MDE, focus on models as primary artifacts (Fig. 1.2).

Models are defined in (semi-)formal languages, that are typically machine-understandable and drawn with the support of tools. Other artifacts are derived through defined transformations: *Model-to-Model* transformations (M2M), or *Model-to-Text* transformations (M2T) from models to textual documents, source code or testing artifacts (such as test cases and test scripts).

As argued by Kent [12], MDE approaches, in general, can identify different levels of decomposition and can employ ad hoc or domain-specific languages for models and transformations, whereas MDA is bound to OMG's standards.

Figure 1.2: Document-centric and Model-centric approaches.

#### 1.1.1 Model-Driven Architecture

The Object Management Group is an international trade association incorporated as a nonprofit corporation in the United States, with affiliate organizations around the globe. In the 90's, OMG standardized the object request broker (ORB) and a suite of objet services. This work was guided by the Object Management Architecture (OMA) that provides a framework for distributed systems and by the Common ORB Architecture, or CORBA, a part of that framework.

OMG first conceived MDA as a technology to overcome the interoperability problems of applications partially addressed by CORBA [13]. Indeed, even if CORBA provided a good solution for the interoperability of applications, it became clear how it is difficult for large enterprises to standardize on different middleware platforms: enterprises have applications on different middleware, that simply have to be integrated even though this process turned out to be expensive and time-consuming. Furthermore, middleware systems continue to evolve and even CORBA could not be a guarantee for next decades. Therefore, MDA was proposed as a better way to reach portability, interoperability and reusability through architectural separation of concerns, in the sight of OMG Vision, that postulates how the myth of a standalone application or standard for developing software as well as for data interchange died.

The recent 2.0 revision of guide of the standard [11] defines MDA as an approach for deriving value from models and architecture in support of the full life cycle of physical, organizational and I.T. systems. MDA became an approach to deal with complexity and interdependence of complex systems to derive value from models and modeling by defining the *structure*, *semantics*, and *notations* of models using industry standards. The value from models is derived from [11]:

• Using Models as communication vehicles. MDA facilitates teams and communities

to come to a common understanding and/or consensus. MDA provides well defined elements, foundation for models and libraries of common vocabularies, rules and processes;

- Derivating artifacts via automated trasformation. The translation can be partial or full and it reduces the time and cost for realizing a design and for changes and main-tenance. Automated derivation involves a platform independent "source model" with some parameters for how that source model is to be interpreted;

- *Performing analysis on models*. Models can be used subject of analysis, including model validation, statistics and metrics;

- Simulating and executing the model. Models as data can drive simulation engines that can assist in both analytics and execution of the designs captured in models;

- Deriving information from models. Well defined models can be used to derive information (such as documentation, derived insights, process playbooks, etc.), new models and other artifacts;

- *Structuring Unstructured Information*. MDA technologies provide a way to define structured representation of these documents.

These values translate in flexibilities during whole development process, parts of these were discussed in [13]:

- **Implementation** new implementation infrastructure (the "hot new technology" effect) can be integrated or targeted by existing designs.

- **Integration:** since not only the implementation but the design exists at time of integration, we can automate the production of data integration bridges and the connection to new integration infrastructures.

- **Maintenance:** the availability of the design in a machine-readable form gives developers direct access to the specification of the system, making maintenance much simpler.

- **Testing and Simulation:** since the developed models can be used to generate code, they can equally be validated against requirements, tested against various infrastructures and can used to directly simulate the behavior of the system being designed.

MDA focuses on intrinsic value of models to increase the abstraction level when developing software, software will be developed by modeling, and models will become code by applying automatic transformations on models. Transformations are not different from language compiler, but are more robust to the change of technologies, because will change the transformation rules but will no change models.

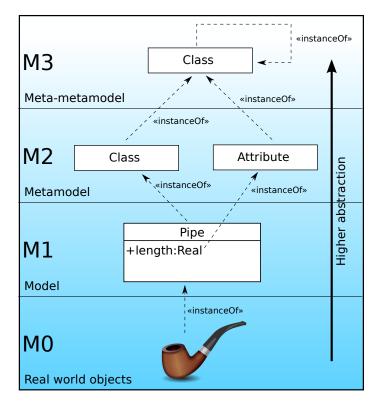

In order to enable (automatic) transformations of models, it has been necessary to introduce mechanisms to reason on modeling itself: this has been done introducing the concept of meta-modeling, i.e., introducing models for modeling languages. These concepts are commons to MDE, but MDA standardized the formalisms to use, so as to have four layer of abstractions (Fig. 1.3):

- M0 is the user data layer, it is the layer at lowest abstraction and the elements are concrete objects of the problem domain.

- M1 is the layer of modeling concepts. Here are the UML models of entities that abstract the user data layer, like UML classes or association. At this level are models defined by software engineers to define the requirements or architecture of the system.

- M2 is UML Metamodel, i.e., M2 defines, through UML, the syntax of UML models in M1, as well as their semantic. For instance, M2 will constraint you to do not use UML links for connecting classes but UML objects. M1 models can be seen as instances of concepts of M2 layer and, by M2, you can check consistence of your UML models.

Figure 1.3: The OMG Modeling infrastructure.

M3 is most abstract layer defined by OMG. At this level is Meta-Object Facility (MOF) language. By MOF OMG can define syntax and semantic for meta-languages. In the MDA, MOF enables to define transformation rules among different models (of M1 layers) that are compliant to different meta-models (of M2 layers).

Using its modeling infrastructure, OMG can define rules to transform models to models (M2M) or model to text (M2T). With M2T transformation, MDE refers to that kind of transformation that produces source code (or less structured documents) from models.

MDA also defines more standards that address the complete development life cycle, covering analysis and design, programming, testing, component assembly as well as deployment and maintenance. One of the characteristics of UML is its capability to be easily extended by mechanisms defined in the standard: by UML *Profiles*, *Tagged Values* and *Constraints*,

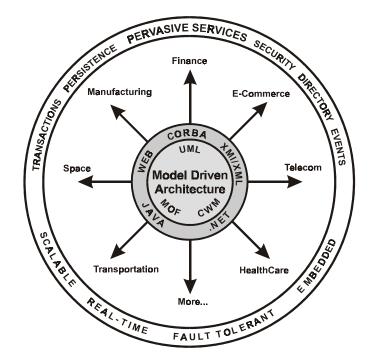

Figure 1.4: Pervasive services and specialized computing environments in the vision of the MDA [14].

custom domain specific languages (DSLs) can be defined, reusing and extending the elements of the UML language.

OMG provided a full set of platform independent pervasive services (Fig. 1.4) that models can exploit. These cover functional and non-functional application requirements ranging from persistence and event handling services to scalability solutions, security and fault tolerance services. Through these, MDA aims at reaching to goal of universal integration. Some of these standards are presented in tab. 1.1. Regarding the inclusion of UML in the standard, the recent revision of MDA, does not require to use UML, but only defined the compliance with the Meta Object Facility (MOF) for the tool compliance *MDA Compliant*.

Finally, MDA models are defined as *information selectively representing some aspect of a system based on a specific set of concerns. The model is related to the system by an explicit or implicit mapping* [11]. Thus, models are often, and preferably, expressed graphically with

| Acronym | Standard                                       | Description                                                                |

|---------|------------------------------------------------|----------------------------------------------------------------------------|

| MOF     | Meta Object Facility                           | Provides means for defining meta meta-languages.                           |

| UML     | Unified Modeling Language                      | Defines a modeling and specification language.                             |

| OCL     | Object Constraint Language                     | A declarative language for describing rules.                               |

| XMI     | XML Metadata Interchange                       | A standard for exchanging metadata information.                            |

| CWM     | Common Warehouse Metamodel                     | Defines specification for modeling metadata in data warehouse.             |

| QVT     | Query View Transform                           | Standard set of languages for model transformation.                        |

| MOFM2T  | MOF Model-to-Text Transfor-<br>mation Language | Specification for a model transformation language (in particular to text). |

| UTP     | UML Testing Profile                            | UML Profile enabling to support V&V activities.                            |

| SPEM    | Software Process Engineering<br>Meta-model     | UML Profile to support constructing process models.                        |

Table 1.1: Common OMG standards in MDA.

drawings, but they can also be textual, even in a natural languages, but it can adopts several notations and formats. For example a model of a software system could include a UML class diagram, E/R (Entity-Relationship) diagrams, and images of the user interface, while a model of a physical system could include a representation of the hardware and physical environment, and a performance simulation.

#### 1.1.2 MDA Viewpoints and Views

Model-Driven Architecture starts with the well-known and long-established idea of separating the specification of the operation of a system from the details on how that system uses the capabilities of its platform. MDA enables to specify a system independently from the platform that supports it, and to transform the system specification into one for a particular platform.

A *viewpoint* specifies a reusable set of criteria for the construction, selection, and presentation of a portion of the information about a system, addressing particular stakeholder concerns [11]; in other words, a viewpoint defines the abstractions to adopt to focus on particular concerns within the system. A *view* is a representation of a particular system that conforms to a viewpoint [11].

In MDA terms, abstraction eliminates certain elements from the defined scope and may result in introducing a higher level viewpoint at the expense of removing detail. A more abstract model encompasses a broader set of systems, whereas a less abstract model is more specific to a single system or restricted set of systems. One important capability of MDA is the automation that provides for the transformation between levels of abstraction by the use of pattern.

MDA specifies three viewpoints, that offers levels of separation of concerns to realize a system. The three viewpoints are the *computation independent viewpoint* (CIV), the *platform independent viewpoint* (PIV) and a the *platform specific viewpoint* (PSV).

- **Computation Independent Viewpoint** The computation independent viewpoint focuses on the environment of the system, and the requirements for the system; the details of the structure and processing of the system are hidden or as yet undetermined.

- **Platform Independent Viewpoint** The platform independent viewpoint focuses on the operation of a system while hiding the details necessary for a particular platform.

- **Platform Specific Viewpoint** The platform specific viewpoint combines the platform independent viewpoint with an additional focus on the detail of the use of a specific platform by a system.

The recent version of MDA standard [11] reduces the emphasis on the CIV, and defines a *platform* as a the set of resources on which a system is realized. This set of resources is used to implement or support the system. For instance, a platform can be the organizational structure or a set of buildings and machines (in case of business or domain platform

| View    | Textual Model                                                                                             |  |

|---------|-----------------------------------------------------------------------------------------------------------|--|

| CIM     | CIM Priority must be given to shipping the oldest articles.                                               |  |

| PIM     | The Articles are ordered according to date for shipment.                                                  |  |

| PSM/OOD | Articles are sorted for shipment() in increasing order, using their attribute date.                       |  |

| PSM/OOP | Use quicksort() to sort Articles, using Articles. Date as sorting key, before passing them to shipment(). |  |

Table 1.2: An example on the MDA views: CIM defines the requirements textually using a vocabulary familiar to domain experts. PIM defines the operations that satisfy the requirement, while PSM refines the PIM adding the messages and the operations to invoke in a Object-Oriented design and implementation.

types); or operating systems, programming libraries, and CPUs (when considering computer hardware and software platform types).

A platform model also specifies requirements on the connection and use of parts of the platform, and the connections of an application to the platform. Example: OMG has specified a model of a portion of the CORBA platform in the UML profile for CORBA. This profile provides a language to use when specifying CORBA systems. The stereotypes of the profile can function as a set of markings. A generic platform model can amount to a specification of a particular architectural style.

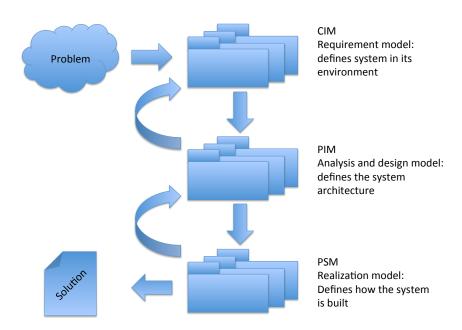

Considering the previous views, MDA defines the *Computation independent Model* (CIM), the *Platform Independent Model* (PIM), and the *Platform Specific Model* (PSM). MDA refines CIM in PIM and in PSM using model transformations during development process (Fig. 1.5).

#### Computation independent Model (CIM)

A Computation Independent Model is a view of a system from the computation independent viewpoint. CIM is at the highest level of abstraction; it neglects the processing and the internal structure of the system and offers a model that is independent by computation details.

Figure 1.5: The MDA Viewpoints.

CIM is also sometimes called a *domain model*, since it offers a vocabulary that is familiar to the practitioners of the domain and is used for specification. Therefore, CIM plays an important role in bridging the gap between those that are experts about the domain and its requirements on the one hand, and those that are experts of the design and construction of the artifacts that together satisfy the domain requirements, on the other.

#### Platform Independent Model (PIM)

A Platform Independent Model is a view of a system from the platform independent *viewpoint.* PIM is a model that focuses on the operations of the system, but abstracts the relations that concern a particular technology or execution platform, such as the hardware interface, the programming language and the middleware. Since a PIM exhibits a specified degree of platform independence so as to be suitable for use with a number of different platforms of similar type.

#### Platform Specific Model (PSM)

A platform specific model is a view of a system from the platform specific viewpoint. A PSM combines the specifications in the PIM with the details that specify how that system uses a particular type of platform. It can be translated into code to provide a partial or total implementation of the system.

#### 1.1.3 UML extensions of interest

Other UML extensions of interest for the thesis are the OMG Systems Modeling Language (SysML) and the UML Testing Profile (UTP), which has been proposed in the context of Model-Driven Testing (MDT).

SysML is a general-purpose modeling language published by OMG [15] for system engineering, that provides specific support for capturing functional and performance requirements, quantitative constraints, and information flows.

While UML is more software-centric, SysML supports the specification, analysis, design, verification and validation of a wide range of complex systems, that include hardware, software, processes, personal and facilities. SysML partially overlaps with UML 2.0 (Fig. 1.6), it reuses a subset of UML 2 (namely, UML4SysML) but provides additional extensions which have no counterparts in UML or which replace UML constructs as in form of an UML Profile.

One of the main features of SysML is the definition of two new diagram types over UML: *Requirement Diagram* and the *Parametric Diagram*. The first one can be used to model system requirements and their relationships, whereas parametric diagrams can be used for performance and quantitative analysis.

Model-Driven Testing is an MDE activity for V&V [16], it aims at exploiting modeldriven approaches also for testing, i.e., test infrastructure and test cases are generated by transformation of models. To this end, an UML standard profile, the UML Testing

Figure 1.6: The overlap between UML and SysML.

Profile (UTP), can be used to adapt UML as a test specification language: UTP offers the elements to model test architecture, test behavior, test data and test time with UML; by UTP model, test cases and test scripts are derived through transformations, using mapping rules, for instance to Java (using JUnit framework) or TTCN-3. Test cases can be generated automatically starting by behavioral diagrams, such as sequence diagrams, state machines or activity diagrams.

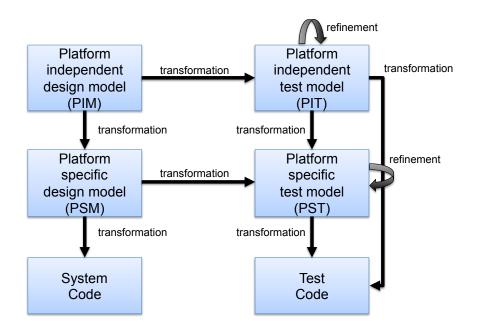

The viewpoints of MDA have also been applied for MDT. The study [17] introduces the concepts of *Platform Independent Test Model* (PIT) and *Platform Specific Test Model* (PST) to separate the test aspects for the general business logic from the platform and technology dependent features of the SUT: this enables to better reuse of testing artifacts for the deployment on multiple target platforms. PIT an PST (skeletons) can be obtained by transformations of PIM and PSM. Test code can be generated by transformation of PIT and PST (Fig. 1.7).

The approach has been extended in [18] with the *Computation Independent Test Model* (CIT): according to the author, the CIT derives from the CIM, and models test objectives and test suite structures combined with overall test strategies used in a specific development process.

Figure 1.7: The integration of MDA and MDT proposed by Dai [17].

# 1.2 State of practice of MBE and MDE

Several surveys analyzed the diffusion and the benefits of Model-Based and Model-Driven technologies into industrial practices, after 30 years from the introduction of the first MD tools on the market. However, these analyses are still not enough to get a complete picture about the state of the MD practices. Indeed, an aspect that is often neglected by these surveys is that the utilization of MD techniques is tight dependent on the domain considered in the analysis, which influences the demands of the users as well as the stability of the environment and the availability and maturity of the supporting tools. For instance, if we consider the development of embedded systems, a stabler environment has eased the diffusion of very complex MD tools such as Matlab Simulink or SCADE, that are always evolving in complexity and functionalities since they were introduced on the market, more than twenty and ten years ago. Differently, if we restrict to the general purpose market, the model-driven tools are generally more limited in their scopes, and the unstable environment requires that they evolve rapidly as new technologies emerge. This observation agrees with the findings of past surveys: the results on the adoption of MB and MD in the industries for the general market differ from the ones in the domain of the embedded system. Even if MDE is always perceived beneficial, the benefits are not so evident like in the domain of the embedded system industry.

MDE in the general industry seems no completely mature yet, and partially debated, with no stable tools and many potentials of model-driven approaches to be exploited. Summarizing multiple observations through surveys of past years in general industry, we can conclude that:

- MDE is spreading with the time in industry, but it is still far to be pervasive. It followed the concurrent evolution of the languages (such as UML) and of the tools: in 2005 practitioners were using MBE for conceptual modeling [19], in 2008 models-centric approaches were perceived better than code-centric ones in most of tasks [20], in 2010 and 2011 MDE has been widely observed in diverse range of industry [21, 22, 23, 24, 25, 26, 27, 28], despite there are many problems and no general and common consensus with these approaches;

- models are mainly used for design and documentation, while the benefits of advanced techniques (such as code generation, test case generation, or model animation) are lowly exploited: models are introduced mostly as an enabling technology inside the process, to enable business that otherwise would not be possible [21, 22, 23];

- UML is gaining the market<sup>1</sup>, but the tools are no mature yet, they are considered one of the biggest problem by the industry, that is worried by the easiness of their usage, the vendor lock-in problem, and the interoperability [25, 26, 27, 28];

<sup>&</sup>lt;sup>1</sup>It is worth to mention, that disagreeing from the previous surveys, the study [29] targeted the use of UML in industry on fifty software designers and found that UML was not used at all or only selectively or informally.

• MDE depends on the business domain and on organizational factors, it need changes inside the personnel, the processes, and company practices: MDE demands for special skills and changes in the importance of developers and software engineers, as retraining software coders to think at a higher level of abstraction which can reveal a difficult task. These aspects have not been well addressed by the MDE, and the current approaches do not adequate to the people, but the people have to adapt to them.

A partially different scenario is observed in the domain of embedded systems, where we can draw the following picture:

- model-based techniques are widely adopted (almost pervasive in automotive domain), and models are used not only for informative and documentation purposes but they were the key artifacts of the development processes [2, 3].

- the needs for introducing models was mainly for shorter development time, and to improve reusability and quality, whereas less than the half had the need to introduce models for exploit formal methods, or because they were required by the standards [2, 3].

- the activities of verification and validation (V&V) had a huge impact by their adoption in the automotive domain [4]: the industry were used to widely exploit model-driven approaches for the early verification of the systems, by techniques such as model reviews, guideline checkers, Rapid Control Prototyping (RCP) and Model- and Softwarein-the-Loop Tests, that lead to better quality, reduced development time, due to the shifting of the costs to the phases of requirement analysis and design;

- according to [30] UML is not used widely, due to short lead-time for the software development, or lack of understanding or knowledge of UML models, however this survey, limited to MDE/MDA in Brazilian industry, does not agree with [2, 3] targeting the European industries of embedded systems. These authors found that the

majority of survey participants were using Matlab/Simulink/Stateflow, followed by Eclipse- based tools. The most used modeling languages were the OMGs ones (UML and SysML);

• as for the general-market domain, in the top shortcomings identified there is in the scarce interoperability and the usability issues of the tools, and the high (initial) efforts to train the developers and to adopt these techniques [2, 3].

Why was the diffusion of MB and MD techniques is different for the general market and for the embedded systems? We claim that this is due to: (i) the different weight of the activities in the development process (more on design and implementation for the general market; and more on analysis and V&V for embedded systems); (ii) the parallel evolution of the code-centric technologies that are available for the development, which raised even more the level of abstraction during the design, and simplified the way the systems are implemented. The hypothesis partially reflects the different focus on the adoption of models in the two domains, since there is more emphasis on design and documentation in the general market, and on the V&V techniques for the embedded systems.

# **1.3** Benefits and Open Challenges

The previous surveys identify the current state of the adoption of the model-driven approaches into the industry by collecting the opinions of the practitioners on the benefits and drawbacks of model-based and model-driven techniques. However, besides these quantitative data, there is the need of empirical studies that analyze qualitatively and critically the merits and faults of model-driven approaches. Indeed, the success or failing factors of MDE are still unclear, and more research is needed [31].

A systematic review of empirical studies on MDE between the period 2000 to June 2007, has been performed by Mohagheghi and Dehlen [8]. MDE can effectively reduce the cost and development time, however it depends on the grade of adoption in the development process: a success story is the one of Motorola [5, 6], that used MDE for more than 15 years in a wide spectrum of activities, ranging from protocol implementations up to hand-held devices or network controllers; they experienced an increase in quality and productivity (ranging from 1.2x to 8x) and an approximately 33% reduction in the effort required to develop test cases.

Motorola could achieve these results, only within a mature process that was supported by own-made translators and tools for the model exploitation. Indeed, one common issue of MDE is the absence of well-defined processes [8, 32, 33], as the application of MDE requires changes in the activities, corporate culture and skills of the employees: many software engineering methods are not fitted to use models as main artifacts, and the environments seems not mature enough. Some previous studies attempted to apply pre-existing processes to MDE, or to create own ones, but MDE shifts the importance of many activities to (automatic) transformation rules, and change consolidated development process is not a naive task. The study [7] reports a successful introduction of a MBE process after four years and three projects had been defined and consolidated: there is the need to look beyond the technical benefits of a particular approach to MDE and instead concentrate on social and organizational issues [23].

Moreover, the process becomes a more difficult problem in safety-critical domain, where compliance with certification standards poses additional requirements on the methodologies for product life cycle. For these kind of systems, the major part of costs are for the activities of verification and validation, so rigorous and well-assessed techniques have to be integrated within the development process for the early detection of faults and to guarantee the quality of the product. In addition, non-functional requirements, such as the safety, the reliability and timing requirements, are a primary concern that have to take into account by these processes: current MDE methodologies does not cope well stringent functional requirements and qualities in current systems, i.e., the ability of these approaches to adapt to rapidly changing hardware and implementation platforms that are highly complex [31].

Parallel to the challenge of the product life cycle, there is the open problem of the supporting tools: they are not mature yet, and influence most of the adoption of MDE. Moreover, the vendor lock-in problem is also perceived as a problem, and the companies prefer to adopt open source solutions or to develop their own tools. Indeed, the tools are not well usable, do not interoperate between themselves, do not keep in synchronization the models at different level of abstractions, are not flexible to collaborative working, and are not suited with the adoption of different models and modeling notations [31]. Thus, model-driven processes have to careful consider the problem of defining the toolchain for supporting the activities.

# Chapter 2

# Literature Review

# 2.1 Model-Driven Processes for Critical Systems

This chapter presents a systematic literature review performed with the goal of investigating current methodologies for the engineering of critical systems. As suggested by the studies on the use of MDE in practice, the process is an important aspect to be considered when adopting model-driven approaches, since it influences on the effectiveness of these techniques.

### 2.1.1 Research questions

The study has been undertaken as a systematic literature review based on the guidelines as proposed by Kitchenham [34]. The focus of our review is on the proposed model-based or model-driven methodologies for the life cycle of critical systems. The research questions addressed by this study are:

- **RQ1.** What is the focus of the studies on MBE/MDE for critical systems, and the relevance of the development methodologies?

- **RQ2.** What are the motivations that lead the research on MBE/MDE development methodologies for critical systems?

- **RQ3.** How does this research benefit from models?

**RQ4.** What are the current limitations of this research?

#### 2.1.2 Search process

The search process was performed using the digital scientific catalog Elsevier Scopus [35], looking for indexed studies in the database until 2016.

According to our focus, we wanted to select paper that cover model-driven processes in safety- and mission- critical systems. Thus, the query retrieved scientific papers using in the title, abstract or keywords the terms "model-based", and "safety-critical system", including synonyms of both terms. We limited our analysis to the publications in the field of Computer Science and Engineering:

```

TITLE-ABS-KEY

```

```

(

OR "Model based" or "MBE" )

(("Model-based"

OR

OR "Model driven"

("MDE"

OR

"Model-Driven"

OR

"MDA"))

AND

(( "safety" OR "critical" or "safety critical"

OR "safety-critical"

OR "mission" OR "mission-critical")

PRE/0 ("system" OR "systems"

OR "domain" OR "domains"

OR "application" OR "applications"))

) AND PUBYEAR <

2016

```

#### 2.1.3 Inclusion and exclusion criteria

Each study was selected manually by the author, based on the analysis of the title and of the paper abstract. We excluded those studies whose focus is not about model-driven or model-based approaches for the engineering of critical systems. In other words, we filtered out the papers not concerning the life cycle of software (and hardware) systems. Similarly, we discarded retracted articles, and duplicates.

### 2.1.4 Paper classification

The scientific papers have been manually classified, according to their main contribution, as reported in title and in the abstract. We adopted the following classification:

- **Typology** We differentiated the studies by their main class of focus, according to the categories listed in Tab. 2.1. Since this classification is not orthogonal, we preferred that class more specific for the work. The typologies can be divided into two main branches: *Investigations* and *Contributions*, the latter including *Life Cycles*, *Non-Functional Requirements* and *Infrastructure*.

- **Modeling Scope** We identified if the studies refer to *Model-Based* or *Model-Driven* approaches, and if they are based on OMG standards. We also classified the scientific papers by *Model-Based Testing* or by *Model-Driven Testing*.

- Industry Domain We assigned the studies to an industrial domain, according to their scope, i.e., if they focus on one particular type of systems. The Industry domain classes considered are: Aerospace, Automotive, Avionics, Embedded, General-Market (such as, web applications), Railway, Others, and Unspecified.

#### 2.1.5 Data collection

From each study, we extracted the following data:

- the title, authors, abstract, keywords, and publishing year;

- the source and document type (article, conference paper, etc.);

- the category of the main contribution;

- the kind of techniques based on the models adopted by the study;

- the domain referred by the work.

## 2.2 Search results

The query provided 858 results: analyzing by authors and titles the results, 16 duplicates were removed. Then, the remaining 842 results were analyzed manually by the author according to the inclusion/exclusion criteria.

The filtering led to the selection of about 50% of the papers, i.e., 423 results were later classified according to the typology categories listed in Table 2.1, as perceived by the reviewer by the analysis of the title and of the abstract.

In order to answer to research questions RQ.2-RQ.4, we reviewed again the studies belonging to the classes of Development Methodologies, Survey, Literature Review and Experiences, selecting and analyzing the relevant ones by the analysis of the full paper. However, we excluded eleven papers by this analysis: the studies written by the author of this thesis, and the papers whose full text could not be retrieved. We could not access to the studies available on SAE International [36], InderScience [37] or AHS [38].

# **RQ1.** What is the focus of the studies on MBE/MDE for critical systems, and the relevance of the development methodologies?

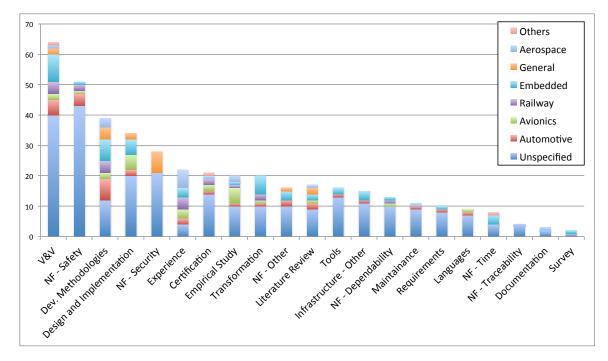

Sorting the typologies of papers by number of studies, the top five typologies (that account for the 51.1% of all the works) are Verification and Validation (15.1%), Safety (12.1%), Development Methodologies (9.2%), Design and Implementation (8.0%), Security (6.6%). The data are tabulated (Tab. 2.1) and represented graphically (Fig. 2.1). These results show how the activities of V&V, Safety and Development Methodologies have deserved primary focus by previous research.

|                | Typology             | Description                                                                                       | Size | %        |

|----------------|----------------------|---------------------------------------------------------------------------------------------------|------|----------|

| Investigation  | Survey               | Investigation conducted by interviews.                                                            | 2    | 0,5      |

|                | Literature Review    | Investigation conducted by analyzing scien-<br>tific literature.                                  | 17   | 4,0      |

| ves            | Empirical Study      | Investigation conducted by experiments.                                                           | 20   | 4,7      |

| In             | Practical Experience | Report on experiences.                                                                            | 22   | $^{5,2}$ |

| Life cycle     | Dev. Methodologies   | Contribution regarding MB, MD methodolo-<br>gies or on the development process.                   | 39   | 9,2      |

|                | Requirements         | Contribution regarding requirements analy-<br>sis or management, or validation at early<br>stage. | 10   | 2,4      |

|                | Design and Impl.     | Contribution limited to the design or imple-<br>mentation of the product.                         | 34   | 8,0      |

|                | V&V                  | Contribution regarding activities of Verifica-<br>tion and Validation.                            | 64   | 15,1     |

|                | Certification        | Contribution focused on easing or supporting the certification.                                   | 21   | 5,0      |

|                | Maintenance          | Contribution on the maintenance or post-<br>deploy activities.                                    | 11   | 2,6      |

|                | Documentation        | Contribution for the documentation of the system.                                                 | 3    | 0,7      |

|                | NF Dependability     | Contribution for the dependability of the system.                                                 | 13   | 3,1      |

| lal            | NF Security          | Contribution for the safety of the system.                                                        | 28   | 6,6      |

| Non Functional | NF Traceability      | Contribution on improving the (model) traceability.                                               | 4    | 0,9      |

| n Fun          | NF Time              | Contribution for performance or timing is-<br>sues in real-time systems.                          | 8    | 1,9      |

| Non            | NF Safety            | Contribution on the safety requirements of the systems.                                           | 51   | 12,1     |

|                | Others               | Contribution not falling in one of the previ-<br>ous NF typologies.                               | 16   | 3,8      |

| cture          | Transformation       | Contribution on model transformation rules.                                                       | 20   | 4,7      |

|                | Tools                | Contribution on tools for model-based environment.                                                | 16   | 3,8      |

| L U            | Languages            | Contribution on languages for modeling.                                                           | 9    | 2,1      |

| Infrastructure | Others               | Contribution on supporting environments<br>or specific features for the development or<br>V&V.    | 15   | 3,5      |

Table 2.1: The typologies adopted for classifying the studies.

Figure 2.1: Distribution of reviewed papers by Typology and Industry Domain.

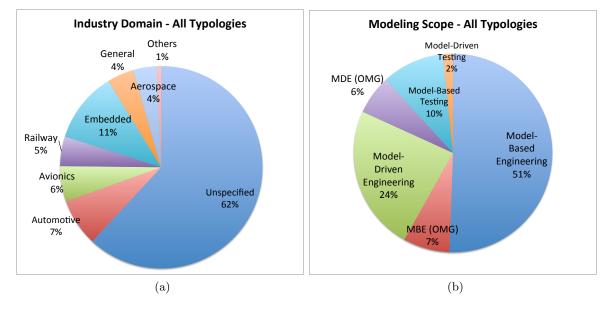

By analyzing the industry domains (Tab. 2.2, Fig. 2.2), we can find some interesting points:

- most of papers added contributions considering Embedded and Automotive domains, followed by Avionics and Railway. This is consistent with the fields where MBE techniques are more spread in practice;

- the papers in the class of Security only considered the General Market Industry: this can suggest that security concerns are scarcely addressed in other industrial domains;

- the model transformations have been discussed mainly for domain of embedded systems;

- the studies on the certification encompass all the domains excluding Embedded and General Market domain. This result is consistent with the domains where certification is pursued.

Fig. 2.2 also depicts the Modeling Scope of reviewed studies. Model-Based approaches are more common than model-driven approaches (MBE and MBE (OMG), total 58%, vs. MDE and MDE (OMG), total 30%). OMG standards were adopted by the 13% of the studies. This can be symptom that OMG standards or the OMG supporting tools are not mature yet to be object of more attention by research.