UNIVERSITÀ DEGLI STUDI DI NAPOLI FEDERICO II Dottorato di Ricerca in Ingegneria Informatica ed Automatica

## ON THE QUALITY OF FAULT INJECTION FOR OFF-THE-SHELF COMPONENTS IN SAFETY-CRITICAL SYSTEMS

ANNA LANZARO

Tesi di Dottorato di Ricerca (XXVI Ciclo) Marzo 2014

Il Tutore Prof. Domenico Cotroneo Il Coordinatore del Dottorato Prof. Francesco Garofalo

## Dipartimento di Ingegneria Elettrica e delleTecnologie dell'Informazione

🖃 Via Claudio, 21 - 80125 Napoli - 🕿 [+39] 081 76 83813 - 🗐 [+39] 081 76 83816

## ON THE QUALITY OF FAULT INJECTION FOR OFF-THE-SHELF COMPONENTS IN SAFETY-CRITICAL SYSTEMS

By Anna Lanzaro

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY AT UNIVERSITA' DEGLI STUDI DI NAPOLI FEDERICO II VIA CLAUDIO 21, 80125, NAPLES, ITALY MAY 2014

© Copyright by Anna Lanzaro, 2014

## Acknowledgements

First, I would like to thank my advisor prof. Domenico Cotroneo for his professional support, for his constantly encouragement and, above all, for his trust in me.

A special thanks goes to Roberto Natella, who was a great co-advisor during my master degree and he continued to patiently support me during these three years. I am really glad and I feel honoured to work with him.

I also want to thank Antonio Pecchia, who gave me important and valuable advises during my PhD. He is my colleague, but he is especially a good friend.

Concluding, I would thank both MOBILAB and CINI groups, including people who were in our lab since the beginning of my experience and the ones who have just arrived. I wish them all the best.

Anna

# Table of Contents

| Li       | st of | Tables | 5                                                   | vii    |

|----------|-------|--------|-----------------------------------------------------|--------|

| Li       | st of | Figure | es                                                  | viii   |

| 1        | Intr  | oducti | ion                                                 | 1      |

|          | 1.1   | Thesis | s contributions                                     | <br>7  |

| <b>2</b> | Off-  | The-S  | helf Components in Safety-Critical Systems          | 12     |

|          | 2.1   | Introd | luction                                             | <br>12 |

|          | 2.2   | Off-Tł | ne-Shelf Components: Definitions and Classification | <br>13 |

|          | 2.3   | OTS (  | Components and Safety Standards                     | <br>14 |

|          | 2.4   | Testin | g OTS-based Systems                                 | <br>17 |

|          |       | 2.4.1  | Dependability: Basic Concepts                       | <br>18 |

|          |       | 2.4.2  | Fault Injection Testing                             | <br>19 |

| 3        | Ach   | ieving | Accuracy in Binary Code Mutation                    | 23     |

|          | 3.1   | Introd | luction                                             | <br>23 |

|          | 3.2   | Backg  | round and Related Work                              | <br>25 |

|          |       | 3.2.1  | G-SWFIT                                             | <br>29 |

|          |       | 3.2.2  | SAFE                                                | <br>30 |

|          | 3.3   | Exper  | imental Evaluation of Binary Fault Injection        | <br>32 |

|          |       | 3.3.1  | Fault Matching                                      | <br>35 |

|          |       | 3.3.2  | Fault Sampling                                      | <br>37 |

|          |      | 3.3.3  | Case Study                                                                                                                  |

|----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------|

|          |      | 3.3.4  | Results                                                                                                                     |

|          | 3.4  | Syster | natic Testing of Binary Fault Injection                                                                                     |

|          |      | 3.4.1  | Test-suite Generation                                                                                                       |

|          |      | 3.4.2  | Test-suite Execution, Comparison and Detection of Inaccuracies 67                                                           |

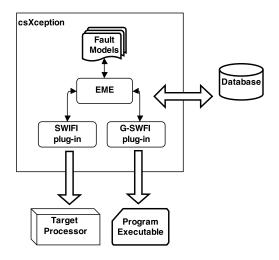

|          |      | 3.4.3  | The csXception <sup>TM</sup> suite $\ldots \ldots 71$ |

|          |      | 3.4.4  | Test Planning                                                                                                               |

|          |      | 3.4.5  | Results                                                                                                                     |

|          | 3.5  | Summ   | ary                                                                                                                         |

| 4        | Ach  | ieving | Representativeness in Interface Error Injection 84                                                                          |

|          | 4.1  | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $84$                                                                    |

|          | 4.2  | Backg  | round and Related Work                                                                                                      |

|          | 4.3  | Propa  | gation of Errors at Component Interfaces                                                                                    |

|          |      | 4.3.1  | Propagation analysis approach                                                                                               |

|          |      | 4.3.2  | Component fault injection                                                                                                   |

|          |      | 4.3.3  | Results                                                                                                                     |

|          | 4.4  | Summ   | ary                                                                                                                         |

| <b>5</b> | Soft | tware- | Implemented Fault Injection in the Multicore Era 117                                                                        |

|          | 5.1  | Introd | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $117$                                        |

|          | 5.2  | Multio | core in safety-critical systems                                                                                             |

|          | 5.3  | Backg  | round and Related Work                                                                                                      |

|          |      | 5.3.1  | Software-implemented Error Injection for Multicore                                                                          |

|          |      | 5.3.2  | Case Study                                                                                                                  |

|          |      | 5.3.3  | Campaign $\#1$                                                                                                              |

|          |      | 5.3.4  | Campaign $#2$                                                                                                               |

|          | 5.4  | Emula  | ting Hardware Errors in Virtualized Systems                                                                                 |

|          |      | 5.4.1  | Case study                                                                                                                  |

|          |      | 5.4.2  | Campaign 1                                                                                                                  |

|          |      | 5.4.3  | Campaign 2                                                                                                                  |

|   | 5.5 Summary                 | 143 |

|---|-----------------------------|-----|

| 6 | Conclusions and Future Work | 144 |

| в | bliography                  | 150 |

# List of Tables

| 3.1 | Fault Types (see also [36])                                             |

|-----|-------------------------------------------------------------------------|

| 3.2 | Classification of Fault Injection Tools                                 |

| 3.3 | Description of OMFC Fault Type                                          |

| 3.4 | Comparison of Average Software Complexity Metrics of Functions in RTEMS |

|     | and CDMS Code                                                           |

| 3.5 | Fault Types of G-SWFIT [36]                                             |

| 3.6 | Constraints of Fault Types in G-SWFIT [36]                              |

| 3.7 | Parameters of the <i>Faultprog</i> random program generator             |

| 3.8 | Test-suites generated by FaultProg                                      |

| 4.1 | Fault types adopted in this study [36]                                  |

| 4.2 | Outcomes of experiments                                                 |

| 4.3 | Distributions of return values in fault injection experiments           |

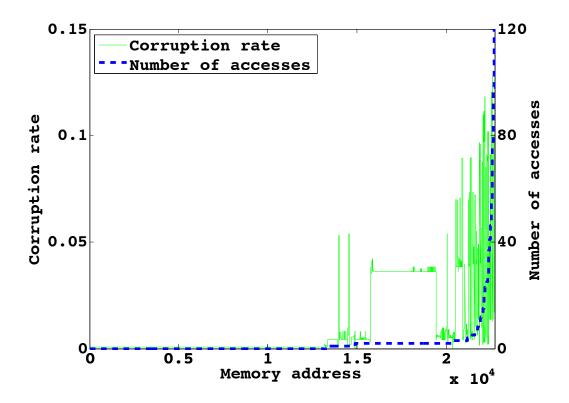

| 4.4 | Correlation between corruption rate and number of accesses              |

| 5.1 | Status Register [15:0]                                                  |

| 5.2 | MCEs injector input                                                     |

| 5.3 | MCE example                                                             |

# List of Figures

| 2.1  | Component and Interface                                                                                                                      | 13 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | General fault injection framework                                                                                                            | 20 |

| 3.1  | Software Fault Injection Techniques                                                                                                          | 32 |

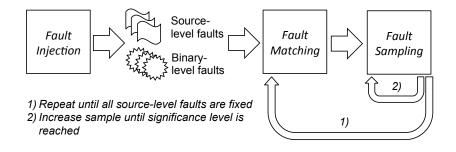

| 3.2  | Overview of the Method for G-SWFIT Evaluation                                                                                                | 35 |

| 3.3  | Fault Matching Procedure                                                                                                                     | 37 |

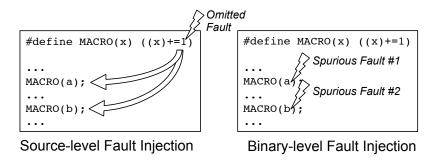

| 3.4  | Examples of Spurious and Omitted Faults Due to C Preprocessor Macro $\ . \ .$                                                                | 39 |

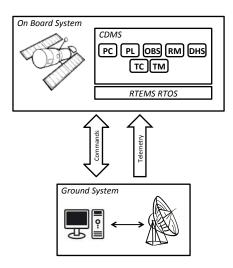

| 3.5  | Architecture of the Case Study                                                                                                               | 42 |

| 3.6  | Distributions of Software Faults at both Binary and Source Code Level                                                                        | 43 |

| 3.7  | Correctly Injected, Spurious, and Omitted Faults                                                                                             | 45 |

| 3.8  | Causes of Incorrect Fault Injection in the Case Study                                                                                        | 46 |

| 3.9  | Number of Faults (Correctly Injected, Spurious, and Omitted) in OS and                                                                       |    |

|      | Application Code                                                                                                                             | 46 |

| 3.10 | Causes of Incorrect Fault Injection in OS and Application code $\ . \ . \ . \ .$                                                             | 48 |

| 3.11 | Spurious MFC Fault in CDMS                                                                                                                   | 51 |

| 3.12 | Omitted MFC Fault in CDMS                                                                                                                    | 52 |

| 3.13 | Omitted MIA Fault in CDMS.                                                                                                                   | 53 |

| 3.14 | Number of Faults (Correctly Injected, Spurious, and Omitted) when Fixing                                                                     |    |

|      | Implementation Issues of the G-SWFIT Tool                                                                                                    | 54 |

| 3.15 | Accuracy of G-SWFIT in the Context of an Embedded Space Software [29]. $% \left[ \left( {{{\mathbf{F}}_{\mathbf{F}}} \right)^{2}} \right)$ . | 58 |

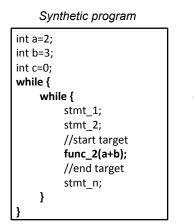

|      | General Structure of a Synthetic Program                                                                                                     |    |

| 3.17 | Proposed Approach                                                                                                                            | 61 |

| 3.18 | Example of a Synthetic Program for Testing MFC Fault Type                                                                                    | 67 |

| 3.19 | csXception <sup>TM</sup> architecture $\ldots \ldots \ldots$    | 72 |

| 3.20 | Distributions of Faults Injected at Binary and Source Code Level 75                          |

|------|----------------------------------------------------------------------------------------------|

| 3.21 | Distributions of Correctly Injected, Spurious and Omitted Faults                             |

| 3.22 | Spurious injections                                                                          |

| 3.23 | Example of synthetic program causing a spurious injection                                    |

| 3.24 | Omitted injections                                                                           |

| 3.25 | Example of synthetic program causing an omitted injection                                    |

| 4.1  | Relationship between component faults and interface errors 90                                |

| 4.2  | Propagation through a library-allocated heap area                                            |

| 4.3  | Propagation through a user-allocated heap area                                               |

| 4.4  | Propagation through a library-allocated heap area, reached through a user-                   |

|      | allocated heap area                                                                          |

| 4.5  | Propagation through a user-allocated local variable                                          |

| 4.6  | Overview of error propagation analysis                                                       |

| 4.7  | Example of reachability graph                                                                |

| 4.8  | Trace pre-processing                                                                         |

| 4.9  | Example of comparison between faulty and fault-free traces                                   |

| 4.10 | Software Fault Injection approach [28,80]                                                    |

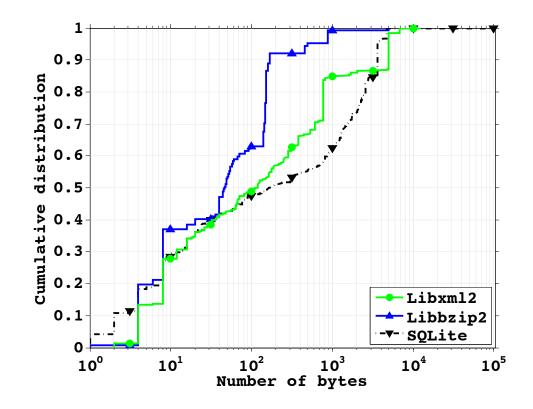

| 4.11 | Cumulative distribution (per library) of the number of corrupted bytes of                    |

|      | interface data                                                                               |

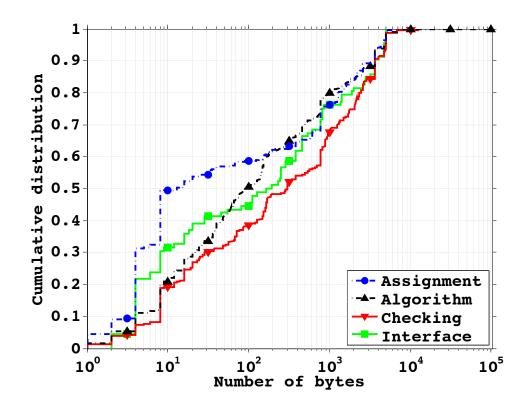

| 4.12 | Cumulative distribution (per fault type) of the number of corrupted bytes of                 |

|      | interface data                                                                               |

| 4.13 | Byte corruption rate and number of accesses for <i>Libxml2</i>                               |

| 5.1  | Proposed Error Injection Framework                                                           |

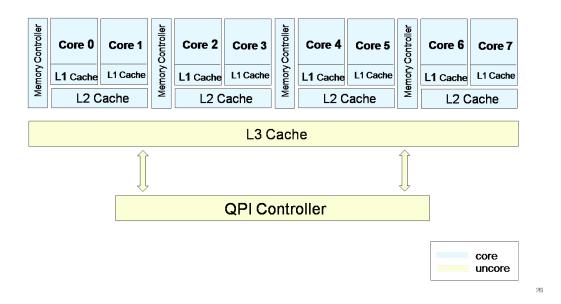

| 5.2  | Intel Core i7 Architectural Block Diagram                                                    |

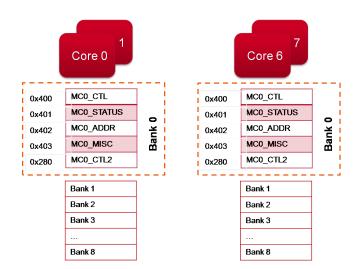

| 5.3  | Machine Check Architecture                                                                   |

| 5.4  | MCE Description File and Severity Levels                                                     |

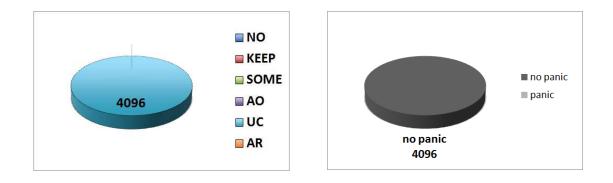

| 5.5  | SER_P=0: Recovery Actions Not Supported by the Processor $\dots \dots \dots \dots \dots 134$ |

| 5.6  | SER_P=1: Recovery Actions Supported by the Processor $\ldots \ldots \ldots \ldots 134$       |

| 5.7  | Severity and Recovery Actions Grouped by Error Categories                                    |

| 5.8  | Severity and Recovery Actions for Campaign $\#2$                                             |

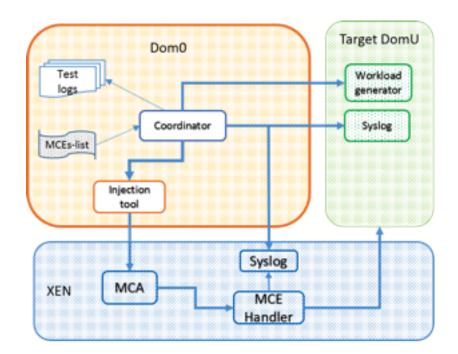

| 5.9  | Injection Framework for Virtualized Systems  |

|------|----------------------------------------------|

| 5.10 | Architecture Framework for Xen               |

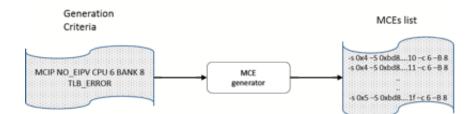

| 5.11 | MCE Generator                                |

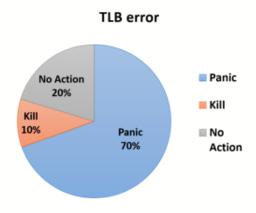

| 5.12 | Recovery Actions for Campaign $\#2$          |

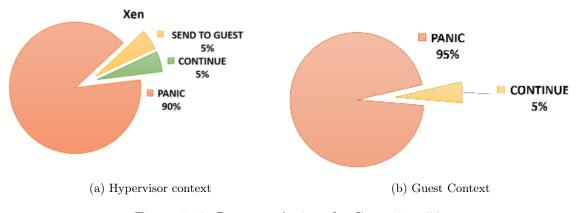

| 5.13 | SER_P=1: Recovery Actions Implemented by Xen |

## Chapter 1

# Introduction

*Fault Injection* (FI) is a family of techniques that emulates hardware and/or software faults by deliberately inserting them into a system component in order to analyze system behavior under faulty conditions, i.e. whether the system can tolerate faults. It is well recognized that Fault Injection is a powerful means for dependability assessment, especially when the system is composed by third-party components, which are often distributed as executables (commercial Off-The-Shelf), being their **source-code not available**.

The integration of hardware and software OTS components is quite common in the development of modern systems. Their adoption is driven by development costs, market pressure, and performance reasons. Similar reasons are behind the adoption of OTS components in safety-critical systems where standards e.g., ISO-26262 [56], IEC-61508 [27], and DO-178B [42] regulate their integration by requiring evidences that OTS components fulfil safety functions. Unfortunately, the lack of documentation and information about the

$\mathbf{2}$

development life-cycle and different operational environments often lead to an improper integration of OTS components, rising the risk of failures [116]. As a consequence, dependability assessment techniques and proper verification strategies are mandatory in order to evaluate system behavior in presence of hardware and software faults.

Regarding the emulation of software faults, fault injection is able to operate at different system levels: at component-level by means of *code mutation* techniques; and at interface-level through *error injection* techniques. Code mutation techniques emulate bugs into a system by mutating the code of a program. Mutations represent software defects, i.e. programming mistakes, to be introduced in the code in order to realistically emulate a faulty software . In the case of OTS-based systems, the injection of programming errors is performed at at binary-level and it presumes that programming constructs used in the source code are identified by looking only at the binary code. Unfortunately, software fault injection (SFI) at binary-level is a difficult and error-prone task due to the complexity of programming languages and of modern compilers, which make difficult and in some cases impossible to accurately recognize where to inject faults. The major concern when injecting software faults at binary-level is to assure that binary-level mutations are accurately performed to emulate programming mistakes, i.e. **SFI has to correctly emulate software faults to an acceptable degree of confidence that a fault injected in the binary**  **code correctly emulates a software defect in the source code**. Inaccuracies in the injection could negatively affect the results of fault injection campaigns leading to erroneously considerations on dependability properties of the system.

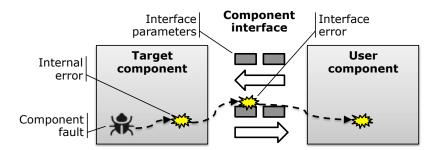

Instead of injecting software faults, *Interface Error Injection* (IEI), which is often adopted in the context of *robustness testing*, mimics the effects (i.e., errors) produced by faults in a component, by *injecting exceptional or invalid values* at the component's interface [48,73,118]. Despite its popularity, the use of IEI for the representative emulation of component faults (as required by dependability assessment strategies [62,78,115]) is questionable. There are not evidences that **the injection of interface errors can realistically emulate faults occurring in the system**. Investigations on the representativeness of interface errors is required in order to perform an effective and representative error injection into the component's interface.

Regarding the emulation of hardware faults, a great variety of fault injection techniques exists. One of the most popular hardware fault injection techniques is known as *softwareimplemented* fault injection, i.e. SWIFI. Based on bit stuck-at and bit-flip models, SWIFI allows the emulation of hardware faults through software by reproducing possible effects of real hardware errors without directly interfering with the system. Although these techniques were successfully employed for the evaluation of system behavior against hardware errors, they could result to be not effective in the case of advanced processors, such as multicore ones. Multicore integrates more cores on the same die that, running in parallel, share many resources (e.g. memory, caches, registers). The complexity of the architecture increases the probability of hardware errors because of the great number of transistors on the same chip. To make processors more reliable, designers and developers have devised many hardwareimplemented mechanisms such as error detection that are able to detect and, in some case, to correct hardware errors. Detected errors are then reported to the upper software layer, i.e. operating system. So that, the complexity is shifted to the software that has to correctly interpret signaled hardware errors and to implement adequate software recovery mechanisms to cope with them. Although SWIFI techniques can be applied also when system integrates multicore processors, fault injection campaign could be very expensive and unfeasible due to the huge number of resources, i.e. possible locations where to inject errors. In fact, the replication of cores means also replicated resources per-core. Moreover, two aspects should be considered when adopting existing fault models. First, single or multiple bit-flip could be automatically corrected by hardware mechanisms and masked to the software affecting the effectiveness of SWIFI techniques. Second, new errors (that were not a concern in single-core architectures) may occur, e.g. errors in the interconnection links between cores make existing SWIFI techniques not representative enough for modern systems. Effective fault injection techniques should evaluate the behavior of software systems deployed on the top of multicore. This is very important also in safety-critical systems where the increasing trend to integrate hardware Off-the-Shelf components is driven by the need of deliver sophisticated and demanding functionalities by assuring innovative solutions, high performance and reduced costs.

Software-based systems in the automotive domain are an example. Modern cars includes many controllers, sensors and actuators connected by different bus for adaptive cruise control with "stop and go" capabilities, stability control, brake assistance or park assistance, etc. To meet the requirements of the modern functionalities, higher performance are demanded, but building ad-hoc advanced hardware components could be very expensive. Exploiting existing components and, above all, taking advantages from technological progress, the integration of hardware Off-the-shelf components seem to be a good choice. Historically, critical embedded systems have been developed using hardware components based on single-core processors, but nowadays they cannot overlook the advances of the micro-controllers market from which general purpose systems such as personal computers, smart-phones and tablet already have beneficed: they have undergone a significant change by replacing single-core processors with multi-core. The migration brings many benefits in terms of performance, power consumption and energy efficiency although it is an awkward activity in critical domains that have to accomplish some strict standards. To exploit the full potential of multi-core, some changes in software are required: tasks should be executed in parallel, i.e. thread level parallelism, to benefit from multi-core. In addition, software running on the top of multi-core has to

take into account architectural changes and improvements: more cores on board connected by links, shared resources, several levels of cache, advanced error handling mechanisms. Unfortunately, we are still far away from the use of parallel programming in critical domains because of problems related to the non-determinism of the execution, to the synchronization and the cooperation between tasks running in parallel.

Nevertheless, multi-core, in conjunction with virtualization [44], can support achieving safety requirements imposed by standards. Virtualization makes it possible running independent applications on each core to ensure properties such as, space and temporal isolation. Furthermore, the inherent presence of replicated cores allows implementing fault-tolerant solutions. Overall these features exacerbate the need for strategies to evaluate dependability characteristics of multi-core systems.

In conclusion, fault injection is widely adopted in the verification and validation of OTSbased systems. Effective FI techniques should guarantee a certain level of **quality**, i.e they must guarantee *representativeness* and *accuracy* properties: **FI techniques should inject in an accurate way faults that are representative.** If these features are not guaranteed, analyses based on fault injection experiments can result to be wrong and, in worst cases, they may contribute to dramatic accidents and economic loss.

### 1.1 Thesis contributions

Considering code mutation, interface error injection and software-implemented fault injection, the main research questions are:

- SFI: Are mutation at binary level accurate enough? How is it possible to validate the correctness of the modifications into the binary code, being sure that injections are correctly performed?

- IEI: Are the existing error model representative? Is an error injected at component interface representative for a real software bug in a component?

- SWIFI: How emulate hardware errors in multicore processors? Are the existing operating systems and hypervisors able to correctly treat errors signalled by hardware error detection and reporting mechanisms of modern processor such as multicore?

This dissertation contributes to the improvement of the quality, i.e. representativeness and accuracy properties, of Fault Injection techniques employed in the evaluation of COTSbased safety-critical systems by proposing:

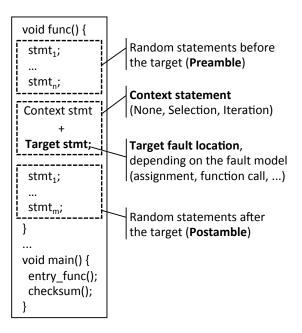

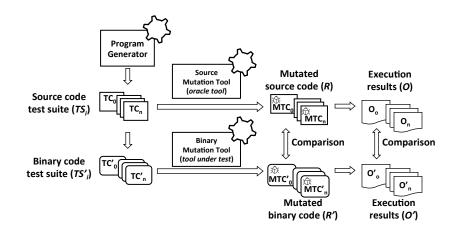

1. A method for testing and improving the accuracy of BCM tools. Software fault injection based on code mutation at binary level requires that programming constructs used in the source code are identified by looking only at the binary code, since the injection is performed at this level. The proposed method is based on the automatic generation of *synthetic programs* that are given as inputs to a BCM tool in order to evaluate its accuracy at performing binary mutations. First, several synthetic programs are generated by encompassing different programming constructs in different contexts (e.g., nested loops, control flow constructs and function calls). Then, the BCM tool is applied on the binary code of the synthetic programs, and the mutations produced by the BCM tool are compared against the source code of the synthetic programs (the analysis of source code serves as a reference, as it does not suffer the limitations of binary level mutation), in order to assess the **ability of the BCM tool to correctly recognize and mutate programming constructs at the binary level**, and to reveal its issues and limitations. In other words, the set of synthetic programs acts as a test suite for evaluating and improving binary-level fault injection and mutation testing tools.

2. A method for analysing error propagation at the interfaces of software components. The method aims at automatically analyzing how software faults in components' code result in errors at components' interfaces, in order to provide some constructive evidence towards more representative IEI techniques. It identifies how faults in software components manifest as interface errors. First, faults are injected in the software component under analysis by using a fault injection technique. Then, it instruments and executes the software component and identifies the effects of injected

faults on the program that uses the component, including the corruption of data structures shared between the program and the component and erroneous return values from function calls.

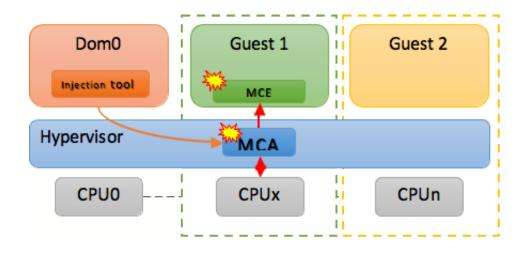

3. A prototype framework for injecting hardware errors in multicore-based architecture The tool aims at injecting hardware errors by exploiting the error reporting architecture implemented in modern processors as multicore in order to asses error handling mechanisms of existing operating systems. Fault injection campaigns have been conducted to test the functionalities of the framework under the Linux OS running on the top of the Intel i7 processor. Based on the same approach, a prototype tool was also proposed to inject errors in virtualized system in order to validate the error handler mechanisms implemented in the hypervisors.

This thesis includes materials from the following research papers, already published in peer-reviewed conferences and journals or submitted for review:

Experimental Analysis of Binary-Level Software Fault Injection in Complex Software,

D. Cotroneo, A.Lanzaro, R. Natella, R. Barbosa, Proc. of 9th European Dependable

Computing Conference (EDCC), May 2012, Sibiu, Romania. (Best Presentation Award)

- Multicore Systems: Challenges for creating a representative fault model for fault injection, N. Silva, R. Barbosa, A. Lanzaro, D. Cotroneo, J. Duraes, DASIA International Space System Engineering Conference, 2012.

- Injecting Machine Check Errors to Explore Dependability Issues of Multicore Systems,

A. Lanzaro, A. Pecchia, M. Cinque, D. Cotroneo, N.Silva, R.Barbosa, Supplemental

Volume of the Proc. of 42nd International Conference on Dependable Systems and

Networks(DSN), 2012.

- A Preliminary Fault Injection Framework for Evaluating Multicore Systems, A. Lanzaro, A. Pecchia, M. Cinque, D. Cotroneo, R. Barbosa, and N. Silva, Supplemental volume of Proc. of 32nd International Conference on Computer Safety, Reliability and Security (SAFECOMP), 2012.

- Tools for Injecting Software Faults at the Binary and Source-Code Level A.Lanzaro,

R.Natella, R.Barbosa, Innovative Technologies for Dependable OTS-Based Critical

Systems Challenges and Achievements of the CRITICAL STEP Project (2013)

- Leveraging Fault Injection Techniques in Critical Industrial Applications A.Pecchia,

A.Lanzaro, As'ad Salkham, M.Cinque, N.Silva, Innovative Technologies for Dependable OTS-Based Critical Systems - Challenges and Achievements of the CRITICAL STEP Project (2013)

An Empirical Study of Injected versus Actual Interface Errors, A. Lanzaro, R.Natella,

S.Winter, D.Cotroneo, N.Suri. Procs of International Symposium on Software Testing and Analysis (ISSTA), 2014

Part of the activities were conducted in collaboration with Critical Software (Coimbra, PT) in the context of the European Project Critical-step "Marie-Curie" Industry-Academia Partnerships and Pathways (IAPP) FP7-PEOPLE-2008-IAPP [2].

## Chapter 2

# Off-The-Shelf Components in Safety-Critical Systems

### 2.1 Introduction

Economical reasons along with technological advances influence the development of systems: the main challenge for developers is to build complex and performing systems by having reduced resources. Traditionally, software-based systems were developed from scratch, but nowadays it is not thinkable because of the high number of functionalities demanded to software. One of the strategy to reduce development costs/time and to exploit new technologies is the integration of components developed by third-party, i.e Off-the-shelf components. In literature, there are many studies that discuss issues related to the selection, integration, maintenance and certification of OTS components in critical systems [69], but they out of the scope of the thesis.

Instead, this dissertation is focused on dependability evaluation of OTS-based systems through adequate and effective testing techniques once OTS components are selected and integrated into safety-critical systems. In particular, this chapter describes the use of OTS components in safety-critical systems by highlighting suggestions provided by the standards about OTS components and testing techniques.

### 2.2 Off-The-Shelf Components: Definitions and Classification

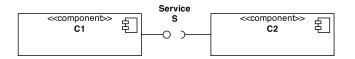

A *component* is an independent and reusable unit whose integration in a system contributes to its functioning. It communicates with the other parts of the system by means of one or more *interfaces*. Interface is an access point by which components provide services that can be required from clients, i.e. other components. For example, in Figure 2.1 component C1 provides the service S. Component C2 is the client that can require the service S by means of its interface.

Figure 2.1: Component and Interface

In hardware engineering, the concept of Off-the-shelf component is well understood (e.g. RAM, CPU, etc.) and and its integration to build more complex systems is a common practice, namely Intellectual property (IP) based development. Instead, for what concern software, an OTS component is not well defined. In literature, there are many and confusing

definitions [107], [86], [113], [19], [16] and the terms Off-the-Shelf (OTS) and Commercial Offthe-Shelf (COTS) are often improperly used. Moreover, depending on the domain, OTS components are also called Government-Off-The-Shelf (GOTS), Military-Off-The-Shelf (MOTS) and Non-Developmental Item (NDI) when components are not-commercially acquired; Open Source Software (OSS) when the source code is available but not modifiable [76]; Software of Unknown Pedigree (SOUP) [18] used in medical domain.

However, according with [107] and [86], we adopt following definitions:

- An *OTS component* is acquired by third-party and it is usually distributed as an executable, so the source code is not available. The latter, when available, cannot be modified.

- A COTS component is an OTS component that (i) is developed by a commercial vendor; (ii) it is available to the general public; (iii) it can be bought (or leased, or licensed) [86].

- An *Open source software* is an OTS component that uses open specifications for interfaces, services, and supporting formats.

### 2.3 OTS Components and Safety Standards

The advantages provided by the OTS integration in critical domains were recognized since 1994 when the US Department of Defence observed that the technology used military systems was 10 years old while new technology emerges every 18-24 months [86]. Since that moment, military systems started the migration to software developed using COTS components. The Department of Defense stated that "to meet future needs, the Department of Defense must increase access to commercial state-of-the-art technology" and "moving to greater use of performance and commercial specifications and standards is one of the most important actions that DoD must take to ensure we are able to meet our military, economic, and policy objectives in the future" [89].

Many recent standards [38] provide guidance on using both hardware and software COTS components as discussed in [71]:

• IEC 61508 [27] is the standard for Electrical/Electronic/Programmable Electronic. It states that the integration of OTS components can bring many advantages, but adequate verification and validation process should provide evidences that components meet safety requirement. Negative effects due to different operational environment, functionalities not required in the new context but implemented in the component, and internal operations of the OTS component not being fully understood should be taken into account during V&V process. It suggests methods such as interface testing, error guessing and seeding (i.e. fault/error injection), and functional testing under environmental conditions.

- MIL-STD-882D [32] is the safety standard adopted in US military and defense domains. It provides suggestions for software development and it requires a safety program to identify hazards and prevent mishaps. Moreover, it recommends additional hazard analyses in case of OTS components by using unit, integration and qualification testing.

- Def Stan 00-55 and 00-56 [101] [102] are safety standards adopted for the development of UK military and defense systems. They suggest system or component evaluation to determine whether they satisfy the requirements. FMEA is used to perform process failure analysis. In particular, Def Stan 00-56 states: "Where COTS or other existing complex electronic elements are used, the Safety Case should detail the processes used for evaluation, validation and implementation of the complex electronic element, the processes used for any bespoke software or hardware (such as software wrappers or hardware interlocks) and any information from the complex electronic element supplier about the development process (where available). In general, the more onerous the safety integrity requirements, the more rigorous and compelling the process evidence that should be provided. For a COTS or pre-existing element, the rigour may have to be provided at the evaluation stage."

- DO-178B [42] is the standard for aerospace domain. It concerns software employed in airborne systems. Both hardware and software components are considered and

studied during safety assessment and verification activities. It suggests the analysis of historical data (e.g. data about the reliability) when adopting existing software in new aircraft and software whose data does not satisfy the guidelines of the standard in order to provide evidences and justify the integration.

### 2.4 Testing OTS-based Systems

Safety standards require evidences that systems are dependable even in presence of OTS/-COTS components, i.e they should tolerate faults. In particular, they suggest the implementation of fault tolerant mechanisms in order to avoid system failures. To accomplish this, these mechanisms have to detect faults and errors that occur during system functioning and perform recovery actions to restore system state. Approach used are based of replication and diversity: examples are Recovery blocks, N-versioning programming.

However, to asses the effectiveness of fault tolerant mechanisms, to evaluate error handlers and error propagations among components, adequate and effective testing techniques are required.

As discussed in 2.2, an OTS components is usually distributed as an executable, i.e. the source code is not available. Due to the nature of OTS components, fault injection techniques seems to be suitable for the aim.

#### 2.4.1 Dependability: Basic Concepts

The fault-error-failure chain expresses the concept that the activation of a fault leads to an error. An invalid state generated by the error may lead to another error or to a failure [14]. In particular:

- Fault is a defect in a system. It can affect software components, e.g. software bugs, and hardware components, e.g. physical faults. If activated, it causes an error.

- Error is the deviation of the system states from a correct state that may lead to a subsequent (service) failure. Errors are dormant if they do not cause service failure, it they manifest at system or component interface, a failure occurs. Errors can propagate from one component to another of the system through their interfaces.

- Failures or service failure is the deviation of the system from the correct implementation of the system function. A failure may occur because the system violates the specification or because the specification is not adequate to describe the behavior of the system. The failure of one or more services implementing system functions make the system operate in a degraded mode.

A system that can avoid service failures that are more frequent and more severe than is acceptable is called *dependable system*. Dependability encompass a set of attributes:

• Availability: readiness for correct service.

- Reliability: continuity of correct service.

- Safety: absence of catastrophic consequences on the user(s) and the environment.

- Integrity: absence of improper system alterations.

- Maintainability: ability to undergo modifications and repairs.

#### 2.4.2 Fault Injection Testing

Fault Injection is a technique that emulates hardware and software faults by deliberately inserting defects into a system component in order to determine how the system behaves when a component fails, i.e. whether the system can tolerate faults. Due to its ability of emulating a malfunctioning in component of target system, FI is widely is considered a valuable dependability assessment approach. It was successfully used for validating fault-tolerance mechanisms by evaluating how a target behaves in presence of faulty components through error detection and handling mechanisms (such as assertions and exception handlers) against component faults [11,67,85]. In [53,78,114], FI techniques were adopted for aiding FME-CAs (Failure Mode, Effects, and Criticality Analysis): Developers can quantify the impact of a faulty component on the overall system (e.g., in terms of catastrophic system failures), and mitigate risks by comprehensively testing the most critical components and revising the system design. Moreover, FI can helps in the context of Dependability benchmarking by providing support for developers to choose among alternative systems or components the one that provides the best dependability and/or performance in the presence of other, faulty, components [62].

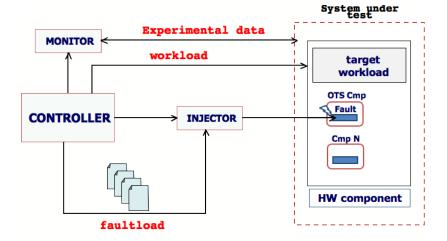

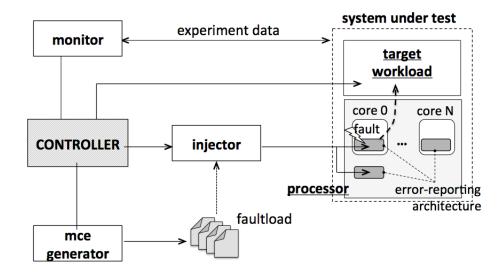

Figure 2.2: General fault injection framework

Figure 2.2 depicts a general framework for fault injection. In the following list, key elements are discussed highlighting the characteristics they should have in order to meet the requirements for an effective, efficient and good quality fault injection.

- The target is the system under test that executes a **workload**, an operating system, an application or a program. A workload should be *representative* for a real system utilization.

- Faultload is the set of faults that will be injected in the target system during the campaign; faults to be injected are defined by a *fault model* describes faults in terms of their type (what to inject), location (where to inject) and trigger (when to inject). It

has to be representative, i.e. a fault has to represent a real defect. *Representativeness* of faultloads is achieved by defining a realistic fault model, instead the *accuracy* is achieved by reproducing this fault model when faults are injected.

- **Injector** is the component responsible of introducing fault into the target. The injector should not distort the actual behaviour of the system under test. The isolation between the injector and the target should be achieved to satisfy the *not-intrusiveness* property.

- Monitor is responsible for collecting data concerning the fault-injection outcomes. Monitor should cope with data loss caused by experiments leading to critical system failures, such as reboot or panic. Again, monitoring and data collection features should not impact the behaviour of the target system. This contributes to *controllability* and *observability* properties.

- **Controller** is the entity responsible for iterating fault injection experiments and coordinating the described components. For each experiment it activates/deactivates the injector module, and stores monitoring data. Moreover, controller should ensure that the workload is actually running at the time injection is performed. It has to fulfil controllability and *repeatability* properties.

This dissertation is focused on the quality of fault injection techniques represented by representativeness and accuracy essential properties for meeting quality requirements. The aim is to evaluate and to improve the quality of existing fault techniques for the assessment of OTS-based systems in safety-critical contexts.

In origin, fault injection techniques were able to emulate hardware faults by physically interfering with the target system through special and expensive devices. To overcome limitations of such techniques, software-implemented fault injection techniques were proposed. They injects hardware faults by emulating the effects of faults (e.g., CPU or memory faults), i.e. corrupting the state of the software using bit-flipping or stuck-at techniques. these techniques are also known as error injection. More recently, software injection techniques emerged. At component level, injection is performed by mutating the source code or the binary code of a component of the target system. Instead, at interface level, software faults are inserted into the component interface of the target.

## Chapter 3

# Achieving Accuracy in Binary Code Mutation

### 3.1 Introduction

Software Fault Injection aims at the realistic emulation of *software faults* (i.e.,  $bugs^1$ ) in a software component to assess the impact of these faults on the system behavior. SFI is assuming an increasing relevance since software faults have been recognized as one of the major causes of system failures [49, 87]. It is used for the experimental validation and improvement of fault tolerance mechanisms and algorithms [10, 85]; it makes possible to analyze worst-case scenarios and the effects of faulty components [78, 114]; it is used in conjunction with dependability forecasting techniques, in order to populate dependability models with measures obtained from experiments [54, 64, 90]; and to benchmark alternative systems or design choices [62]. The realistic emulation of software faults is a key objective to achieve accurate dependability measures and to investigate faulty scenarios that the

<sup>&</sup>lt;sup>1</sup>In this work, we follow the notion that a software fault is a development fault originated during the coding phase [13, 36].

system could face during operation. One of the most popular SFI technique is G-SWFIT (Generic Software Fault Injection Technique), proposed by Durães and Madeira [36]. G-SWFIT injects software faults by mutating the binary executable code of a program. This technique is attractive for practitioners, since it allows to perform Software Fault Injection when the source code is not available, which is often the case when third-party software is adopted. G-SWFIT defines which types of software defects have to be introduced in order to realistically emulate a faulty software, based on recent field data studies that characterized residual software faults in complex systems [25, 36, 105].

An important issue concerning the injection of software faults at binary level is the *accuracy* of the injection campaign, that is, the degree of confidence that a fault injected in the binary code correctly emulates a software defect in the source code. For instance, if we aim to emulate the absence of a variable assignment in the source code, we could remove a "move" instruction at binary level. But, if we consider the emulation of a bug in a C preprocessor macro (i.e., a piece of source code that is replicated several times in the binary code), the problem cannot be resolved by simply looking at the binary code. Therefore, it is important to assess the accuracy of binary-level SFI in order to be effectively adopted in real-world scenarios. Unfortunately, only a few studies evaluated the accuracy of binary-level SFI, which were limited to small programs or to a small number of faults [34, 36, 60], and no previous work analyzed this problem comprehensively.

This chapter provides the state of the art on Software Fault Injection providing more details about fault injection techniques based on code mutation. Then, a method for the experimental evaluation of the accuracy of binary code mutation tool is presented. Then, based on the obtained results, it is described a method developed for the automatic detection of the inaccuracy at binary level.

#### **3.2** Background and Related Work

In order to emulate software faults in fault injection experiments, a model of software faults that can realistically occur in the system under test is required. This property, which is referred to as *representativeness*, is desirable when dependability measures have to be quantitatively assessed, such as coverage factors of fault-tolerant systems [54, 64], which depend on the probability distribution of faults and workloads [90]. Fault representativeness is also important to stimulate the complex failure modes that can be exhibited by a software system or component, which are potentially more subtle than simple process hangs or crashes and are not necessarily known a priori [85, 114]. Field data studies analyzed software faults in complex software systems, and can be used to define software fault models. Sullivan and Chillarege [105] analyzed a large set of software-related failure reports collected from the MVS OS, and proposed a classification scheme for software faults, which are described in a level of detail close to the programming level. That work was later extended in [24] where the Orthogonal Defect Classification (ODC) and the notion of defect type are introduced. This notion points to a high-level classification of faults including Function, Checking, Assignment, Algorithm and Interface faults. ODC was aimed at providing feedback during development; the work presented in [36] extends this level of description and proposes a classification scheme that was precise enough for automated fault emulation (e.g., for the "assignment" class of faults, it specifies if the assignment is an initialization, and if an expression or constant is involved). It also presents a field data study where it is pointed out that most of the software faults found in the field belong to the set of fault types shown in Table 3.1, and that they tend to follow a generic fault distribution.

Table 3.1: Fault Types (see also [36]).

| Fault Type | Description                                            |

|------------|--------------------------------------------------------|

| MFC        | Missing function call                                  |

| MVIV       | Missing variable initialization using a value          |

| MVAV       | Missing variable assignment using a value              |

| MVAE       | Missing variable assignment with an expression         |

| MIA        | Missing IF construct around statements                 |

| MIFS       | Missing IF construct + statements                      |

| MIEB       | Missing IF construct $+$ statements $+$ ELSE construct |

| MLAC       | Missing AND in expression used as branch condition     |

| MLOC       | Missing OR in expression used as branch condition      |

| MLPA       | Missing small and localized part of the algorithm      |

| WVAV       | Wrong value assigned to variable                       |

| WPFV       | Wrong variable used in parameter of function call      |

| WAEP       | Wrong arithmetic expression in function call parameter |

Another aspect affecting the effectiveness of Software Fault Injection is represented by the method adopted to introduce software faults into a system. In fact, SFI requires more complex modifications of the program code/state than simply a bit-flip/stuck-at: the comparison between real software faults and faults injected by SWIFI tools [58, 72] revealed that hardware fault models cannot accurately emulate software faults. The emulation of software faults requires that what it is injected reproduces the intended fault model, i.e.the *accuracy*), in order to correctly evaluate the effects of software faults on the system. Several methods have been devised for emulating software faults, most of them based on rather indirect approaches (i.e., emulating the possible effects of software faults instead of injecting actual faults in the software code).

Past work on software fault injection can be divided in three categories, according to what is actually injected: data errors, interface errors, and code changes (summarized in Table 3.2).

**Data errors.** This approach consists of injecting errors in the data of the target program (i.e., a deviation from the correct system state [13]). This is an indirect form of fault injection, as what is being injected is not the fault itself but only a possible effect of the fault. The representativeness of this type of injection is difficult to assert, as the relationship between data corruption and its possible root-cause (i.e., faults) is difficult to establish. However, data errors are an useful and practical means for inducing software failures and debugging of fault-tolerance mechanisms [114].

Interface errors. This approach is in fact another form of error injection where the

error is specifically injected at the interface between modules (e.g., system components, or functional units within a program). This usually translates to parameter corruption in functions and API, and it is considered a form of robustness testing. The errors injected can take many forms: from simple data corruption to syntactically valid but semantically incorrect information. As with data errors, the representativeness of the errors injected at the interfaces is not clear and there is some empirical evidence that supports the idea that injecting interface errors and changing the target code produces different effects in the target [77]. This approach is complementary to the injection of actual software faults, and it has proven to be useful to find interface weaknesses [67].

**Code changes.** Changing the code of the target component to introduce a fault is naturally the closest thing to having the fault there in the first place. However, this is not easily achieved as it requires to know exactly where in the target code one might apply such change, and what instructions should be placed in the target code. Several works followed this notion, although with some limitations: Ng and Chen [85] and the FINE [64] and DE-FINE [63] tools use code changes (e.g., changing the destination address of an assignment), although their fault model is very simple and its representativeness is not assured. Madeira et al. [72] showed that SWIFI can be used to inject simple code changes in running processes but cannot emulate more complex software faults. The G-SWFIT technique [36] was developed to address software fault representativeness, by injecting software faults according to the set of most common fault types (Table 3.1) observed in field data.

Table 3.2: Classification of Fault Injection Tools

| Category         | Tools                                                                           |

|------------------|---------------------------------------------------------------------------------|

| Data errors      | FIAT [15], FERRARI [61], PSN [114], csXception [21], NFTAPE [103], GOOFI<br>[8] |

| Interface errors | BALLISTA [67], RIDDLE [47], MAFALDA [11], Jaca [74], csXception [62]            |

| Code changes     | Ng and Chen [85], FINE [64], DEFINE [63], G-SWFIT [36]                          |

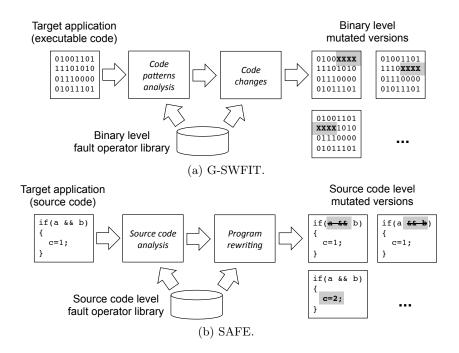

## 3.2.1 G-SWFIT

G-SWFIT injects code changes at the executable (binary) level (Figure 3.1a). It consists of a set of *fault operators* that define *code patterns* (i.e., a sequence of opcodes) in which faults can be injected (e.g., an MIA fault can be injected wherever an IF construct is found), and *code changes* to be introduced (e.g., the removal of instructions related to an IF construct) to emulate software faults<sup>2</sup>. The proposed fault operators inject valid faults in terms of programming language (i.e., mutated code is syntactically correct) and provide a set of constraints to exclude fault locations that are not realistic (e.g., to inject an MIA fault, the IF construct must not be associated to an ELSE construct, and it must not include more than five statements or loops). The description of a fault operator is provided in Table 3.3. As discussed in the rest of this paper, it is not trivial to assure the accuracy of software

<sup>&</sup>lt;sup>2</sup>Each fault operator is related to a specific fault type and is denoted with the "O" prefix (e.g., the OMIA fault operator is related to the MIA fault type).

fault injection at the binary level, due to the gap between software faults at source code level (e.g., defects in a program) and their conversion to binary level (i.e., translation of the faulty code in machine code). The implementation of G-SWFIT and the definition of fault operators are dependent on the hardware architecture, the compiler of the target application, and compiler optimizations, since the binary translation of a programming construct (e.g., an IF construct) varies with the compiler and the hardware platform in which the software can be executed. G-SWFIT was originally implemented and applied on the i386 hardware architecture and the Microsoft Windows environment [35]. The technique has then been ported to inject faults in the bytecode of Java programs [96]. Analysing G-SWFIT, it was considered C language with respect to the PowerPC hardware architecture and the GCC compiler, which has been implemented in a R&D tool by Critical Software.

Table 3.3: Description of OMFC Fault Type

| Example             | function();                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------|

| Example with faults | <i>function();</i>                                                                                            |

| Code pattern        | CALL target-address                                                                                           |

| Code change         | CALL instruction removed                                                                                      |

| Contraints          | Return value of the function must not be used (C01)<br>Call must not be the only statement in the block (C02) |

## 3.2.2 SAFE

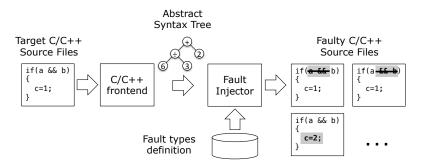

An alternative approach to change the code of a program consists in mutating its source code, and then to compile the faulty source code to obtain a faulty version (Figure 3.1b). This approach has been implemented in a fault injection tool developed by MOBILAB research group [4], namely SAFE (SoftwAre Fault Emulation) tool. The tool adopts the same fault types of G-SWFIT (Table 3.1), including code patterns and constraints, although faults are introduced in the source code instead of the binary code. This tool has different objectives than G-SWFIT, since it cannot perform fault injection when the source code is not available; it is considered as a support to evaluate the accuracy of G-SWFIT. In order to use the SAFE tool, a C preprocessor translates C macros in a source code file (e.g., inclusion of header files) to produce a self-contained compilation unit. A C/C++ front-end then processes the compilation unit, in order to produce an internal representation of the program (Abstract Syntax Tree, AST). The tool searches for suitable fault locations in the AST and applies a fault operator if all constraints are met, e.g., to inject a MIFS fault, an IF construct should not contain more than 5 statements. The tool produces a set of faulty source code files, each containing a different software fault. The faulty version is obtained by replacing a source code file with a faulty file and recompiling the program.

Compared to the binary level approach followed by the original G-SWFIT, the source code level approach assures the accurate emulation of fault types, since full information about programming constructs and variables is available (this information is missing and has to be reconstructed when injecting faults at the binary level). Moreover, injection in the source code is portable among all platforms in which the target program can be compiled,

Figure 3.1: Software Fault Injection Techniques

without any additional efforts to adapt the fault injection tool to different hardware or compilers. The drawbacks of this approach are that it increases experiment time, since the program needs to be compiled after the injection of a fault, and that the approach cannot be adopted when the source code is missing.

# 3.3 Experimental Evaluation of Binary Fault Injection

The experimental evaluation is motivated by the fact that the accuracy of binary-level fault injection is limited by the impossibility to correctly recognize some programming constructs in a binary program. The evaluation of binary-level fault injection in a real-world system contributes to understand the limitations and the accuracy of the results that can be obtained by a fault injection campaign.

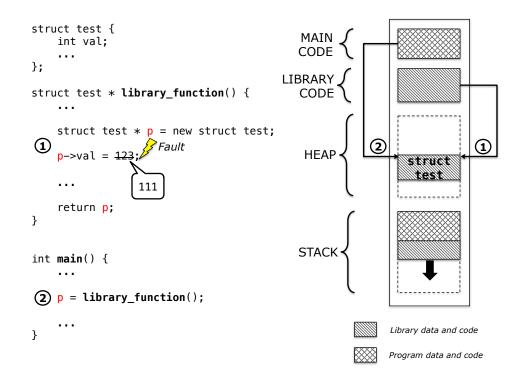

An example of a wrongly injected fault is represented by a C program containing a SWITCH construct with two branches; in some architectures and compilers (this is the case of GNU GCC compiler for PowerPC architectures), the SWITCH may be translated in binary code using the same opcode sequence of an IF-ELSE construct, since they both consist of a logical condition (which is translated using an opcode that compares two values) and two branches (which are translated using branch opcodes). Therefore, a MIEB (see Table 3.1) fault could erroneously be injected in a code location in which there is not an IF-ELSE construct. It may also happen that a code location suitable for fault injection cannot be recognized in the binary code. For instance, a compiler may translate a function call as inline code (i.e., the function call is replaced with the body of the called function); in this case, a fault injection tool would not be able to recognize the function call, thus omitting to inject an MFC fault in that location. The experimental validation aims to assess the relative occurrence of this kind of problems in real-world complex software, in order to evaluate whether G-SWFIT can achieve an acceptable degree of accuracy even in the presence of these problems. Although some of these problems are already known, their extent in large and complex software has not been investigated in previous studies.

The method also aims at pointing out issues that may arise when implementing G-SWFIT, by highlighting cases in which faults are not correctly injected. Binary-level fault injection tools are difficult to implement, since they have to encompass all potential ways in which programming constructs are translated. This problem is further exacerbated if it is considered the complexity of modern CPUs, programming languages and compilers (whose inner working is usually unknown). Thus it is likely that developers may neglect some code patterns, thus leading to design errors in the fault injection tool.

The proposed method evaluates the accuracy of G-SWFIT by comparing the faults it generates with the ones injected in the source code. Indeed, since a software fault is a defect in the code of a program, it is clear that fault injection at source code level is more accurate. Based on this consideration, faults injected by the two techniques are compared and classified faults in the following three categories:

- 1. Correctly Injected faults: correct faults generated by both techniques. The larger is the set of common faults, the higher is the accuracy of G-SWFIT.

- 2. *Omitted faults*: faults injected only at source-code level. They correspond to programming constructs in which a fault could exist, but which have not been identified in the binary code.

- 3. Spurious faults: faults injected only by G-SWFIT at binary level that do not match any fault at source-code level. Therefore, they are not considered as representative software faults.

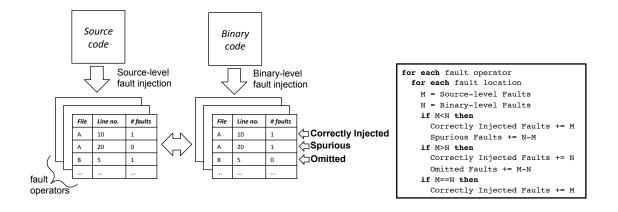

It is important to note that source-level faults can be used as a term of comparison for binary-level faults because (i) the same fault types are adopted for both binary- and source-level fault injection (shown in Table 3.1), and (ii) binary- and source-level faults are injected in every potential location (i.e., fault injection campaigns are exhaustive). The method (depicted in Figure 3.2) consists of two phases, namely (i) automatic matching of binary-level and source-level faults (Section 3.3.1), in order to identify Correctly Injected faults, and (ii) fault sampling and manual analysis (Section 3.3.2), in order to identify which issues affect the accuracy of G-SWFIT. As a real-world case study, it is considered CDMS (Command and Data Management System), a real-time embedded system developed by Critical Software for the space domain (Section 3.3.3).

Figure 3.2: Overview of the Method for G-SWFIT Evaluation

## 3.3.1 Fault Matching

Fault Matching is based on the assumption that if both techniques inject the *same fault type* in the *same location* (e.g., an assignment or function call is removed both in the source code

and in the corresponding location in the machine code), then they are injecting the same fault. It is reasonable to make this assumption since if a fault location is identified both at the binary and source levels, then that fault location is valid and correctly handled. In order to be sure that this assumption holds (and therefore the results are valid), a sample of Correctly Injected faults using the Fault Sampling procedure (explained in the next subsection) manually analyzed. Following this observation, binary-level and source-level faults are compared with respect to their fault types and their locations in the source code (i.e., the source file, the function and the line of code in which a fault is injected). A binary-level fault matches a source-level fault *if they have the same fault type and they are injected in the same code location* (compared using debug symbols in binary code).

The procedure shown in Figure 3.3 has been adopted to identify Correctly Injected faults. If a binary-level fault matches a source-level fault, and only one binary-level fault and only source-level fault exist for the code location under analysis, then the binary-level fault is considered as Correctly Injected. In some cases (e.g., when there are more than one statement in the same line of code), more than one binary-level fault (N), or more than one source-level fault (M) may occur in the same code location. If there are more binary-level faults than source-level faults in the same location (N > M), then there are MCorrectly Injected faults, and N - M Spurious faults. Similarly, if source-level faults are more than binary level faults (M > N), then there are M - N Omitted faults. It follows that if a binary-level fault does not match any source-level fault, then it is considered a Spurious fault, and that if a source-level fault does not match any binary-level fault, then it is considered an Omitted fault. In the examples of Figure 3.3, the proposed procedure identifies one Correctly Injected fault (location A-10), one Spurious fault (location A-20), and one Omitted fault (location B-5).

Figure 3.3: Fault Matching Procedure

#### 3.3.2 Fault Sampling

After the Fault Matching procedure, it is performed a detailed analysis of faults in order to investigate the causes of Spurious and Omitted faults, and to verify that Correctly Injected faults are actually correct. Moreover, the aim is to understand whether Omitted and Spurious faults are due to inherent limitations of G-SWFIT or not. Indeed, these faults may occur due to design issues in G-SWFIT as previously discussed; the identification of these issues is useful to provide guidelines for improving G-SWFIT, and to obtain a more precise

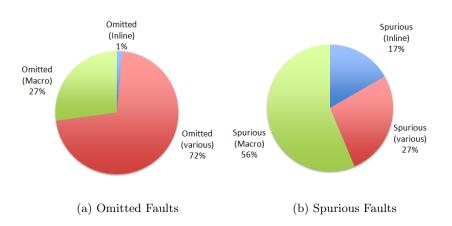

- 1. C preprocessor macros. When the G-SWFIT technique was proposed, preprocessor macros have been recognized as a frequent cause of Omitted and Spurious faults [36]. A preprocessor macro consists of a piece of code that is replicated for each time the macro is referred within the program. Therefore, when a preprocessor macro has a software fault, the faulty code is replicated several times in the binary code. Since the binary code lacks information about macros, G-SWFIT cannot recognize that macro code is replicated elsewhere within the program: therefore, a Spurious fault is injected for each replica of the macro, and source-level faults that could be injected into macro represent Omitted faults since G-SWFIT cannot correctly injected them (see also Figure 3.4).

- 2. Inline functions. In a similar way to preprocessor macros, inline functions are replicated each time the function is called within the program. Since G-SWFIT does not recognize inline functions within binary code, they lead to Spurious and Omitted faults as well.

- 3. Various causes. This category includes all the other causes of Spurious and Omitted faults that are not related to macros or inline functions.

4. Issues in the SAFE tool. Even if source-level fault injection can be considered accurate, it is not excluded the possibility that the adopted source-level fault injection tool could inject faults incorrectly. Therefore, during the manual analysis, it is also looked for issues in the SAFE tool that caused faults to erroneously appear as Spurious or Omitted faults. Since it is required to assure that source-level faults are correctly injected, fixes were made in the SAFE tool when an issue is found and repeat the whole analysis (including both Fault Matching and Fault Sampling) until this category becomes empty.

Figure 3.4: Examples of Spurious and Omitted Faults Due to C Preprocessor Macro

Because of the high number of the generated faults, the manual analysis is conducted on a sample of faults and then conclusions are drawn about the whole set of faults. In order to generalize the results from the sample, it was addressed the problem of choosing a sample of appropriate size, such that it could be considered representative of a population with more than two categories (i.e., a multinomial distribution, where it is defined  $\pi_i$  as the proportion of the *i*th category). The sample should be large enough to assure that all of the estimated proportions  $\pi_i$  are within a given confidence interval with significance level  $1 - \alpha$ .

Assuming that the population and the sample are large enough to use the normal approximation, the probability  $\alpha_i$  that the proportion  $\pi_i$  lies outside an interval of width  $2d_i$  is given by (see [110] for more details about sampling)

$$\alpha_i = \Pr\left\{ |Z_i| \ge d_i \sqrt{n} / \sqrt{\pi_i (1 - \pi_i)} \right\}$$

(3.1)

where  $1 \leq i \leq k$  and  $Z_i$  is a standard normal random variable. By Bonferroni's inequality [110], the probability that one or more of the k estimates will fall outside its interval will be less than or equal to  $\sum_{i}^{k} \alpha_i$ . Equation (3.1) allows to assess if the sample size is large enough to achieve accurate results. If  $\sum_{i}^{k} \alpha_i > \alpha$ , then a larger sample size is required, otherwise the estimated proportions are considered accurate.

This method was applied to the populations of Omitted and Spurious faults by considering k = 4 categories (C preprocessor macros, inline functions, various causes, issues in the SAFE tool), assuming a confidence interval of half-width  $d_i = 0.05$  and a significance level  $1 - \alpha = 0.9$ . This method was also applied to the population of Correctly Injected faults, in order to analyze whether they are truly correct or not (k = 2 categories are considered). For each population, a sample of 5% of faults it is extract and manually analyzed in order to obtain an initial estimate of the proportions; the sample size is gradually increased and analyzed until the required significance level is reached.

## 3.3.3 Case Study

The case study is a satellite data handling system named Command and Data Management System (CDMS). A satellite data handling system is responsible for managing all data transactions (both scientific and satellite control) between ground system and a spacecraft (Figure 3.5), based on the ECSS-E-70-41A standard [39] adopted by the European Space Agency. In this system, a space telescope is being controlled and the data collected is sent to a ground system. As shown in the Figure, the CDMS, which executes on the spacecraft (*on-board system*), is composed by several subsystems: the TC Manager receives a series of commands from the ground control requesting telemetry information; the TM Manager sends back telemetry information for each command sent; the other modules (PC, PL, OBS, RM, DHS) perform tasks for the data management and the telescope handling. The importance of the *accuracy* of SFI in mission-critical systems like CDMS has been demonstrated in [78], in which two OSs (RTLinux and RTEMS) were compared with respect to the risk of failures of the CDMS due to OS faults, in order to select the most reliable OS for this scenario.

The CDMS application was developed in C and runs on top of an open-source, real-time operating system, namely RTEMS<sup>3</sup>. The CDMS makes use of the RTEMS API for task management, communication and synchronization, and for time management. This software

<sup>&</sup>lt;sup>3</sup>http://www.rtems.org

Figure 3.5: Architecture of the Case Study

system is compiled to run on a PowerPC hardware board by using the GCC compiler and disabling compiler optimization settings, which is the setup currently supported by the G-SWFIT tool.

The analysis is focus on faults injected in both the OS (i.e., RTEMS) and application (i.e., CDMS) code. We only consider the code which is actually compiled and linked in the executable running on the on-board system. A small part of the code (1.90%), which is written in assembly language to provide board-specific support, is not targeted by our source-level fault injection tool, but its influence on the results can be considered negligible.

## 3.3.4 Results

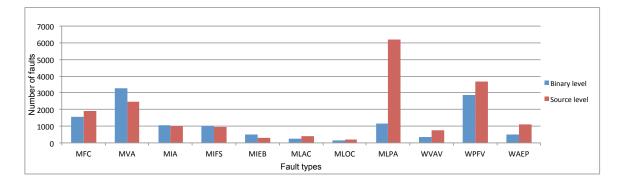

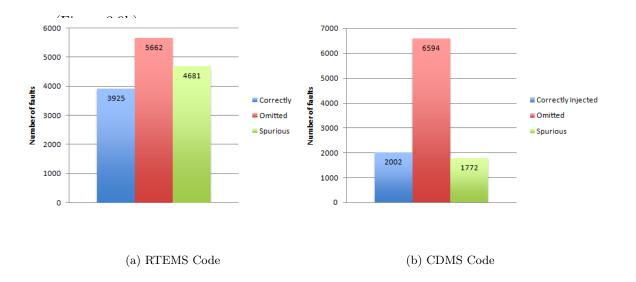

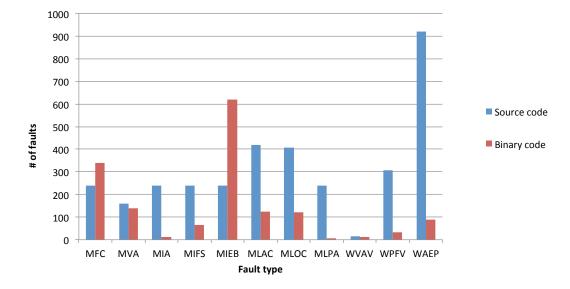

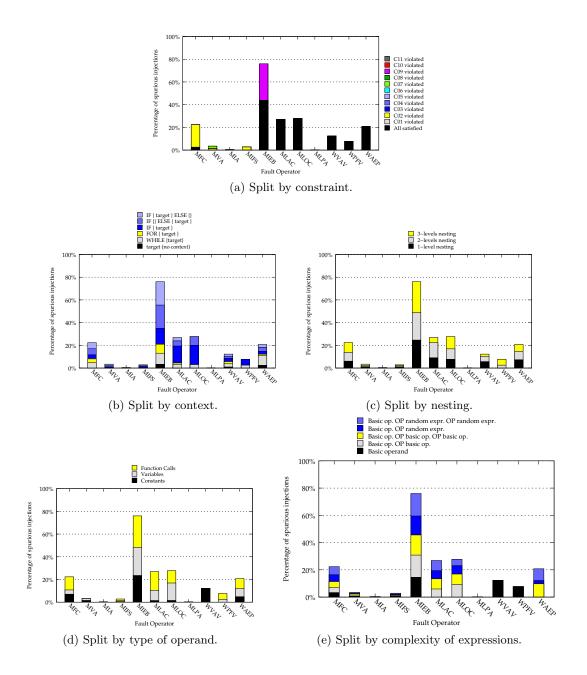

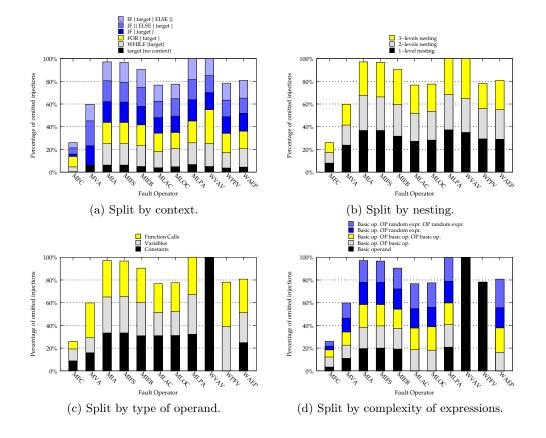

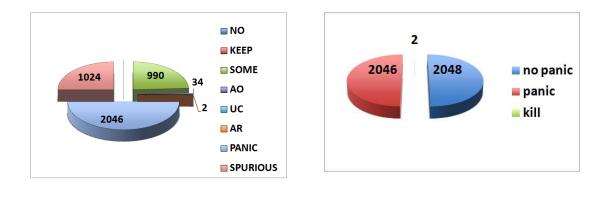

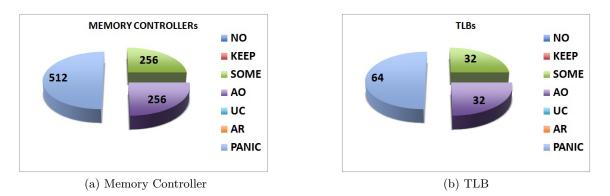

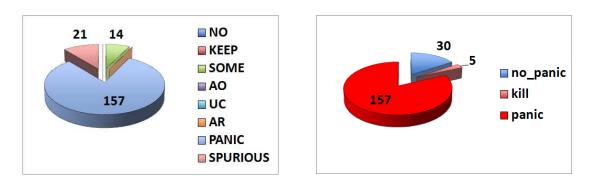

In this section, software faults injected at the binary and source-level in a complex case study are analyzed using the method proposed in Section 3.3. Faults at the binary level were generated with the G-SWFIT technique, by using a R&D prototype tool provided by Critical Software company. Faults at the source code level were generated using the SAFE fault injection tool (described in Section 3.2.1). In total, 18,183 source-level faults and 12,380 binary-level faults were generated, respectively. Their distribution across fault types is shown in Figure 3.6. The two distributions exhibit noticeable differences: more sourcelevel faults are injected with respect to some fault operators (such as OMLPA, OWVAV, OWPFV, and OWAEP), whereas in other cases more binary-level faults are injected (such as OMIEB and OMVA, where the latter groups together the OMVAV, OMVIV, and OMVAE operators).

Figure 3.6: Distributions of Software Faults at both Binary and Source Code Level

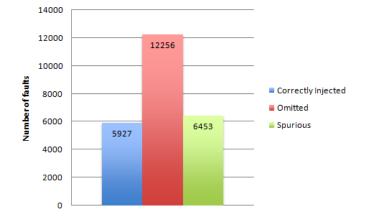

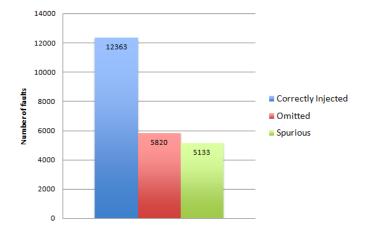

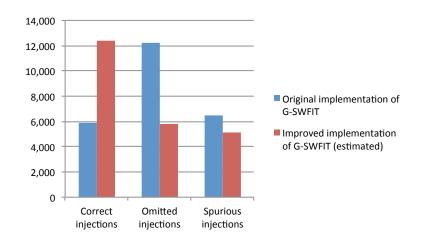

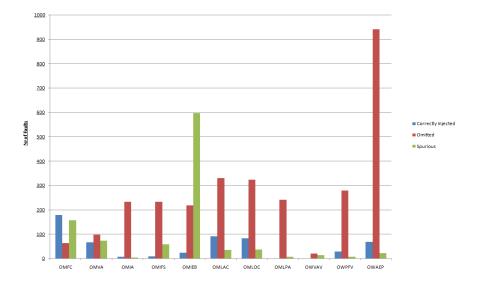

The Fault Matching procedure (Section 3.3.1) identified the subset of Correctly Injected faults (i.e., common to both techniques) that are analyzed in order to assure the correctness of the method. Correctly Injected faults have been sampled (see Section 3.3.2), and then compared by looking at i) the faulty binary-code generated by G-SWFIT, and ii) the one produced by faults injected in the corresponding source-code locations. This analysis revealed that the binary-level faults match the source-level faults for each fault types and for each sampled faults, except the OWPFV operator. It is found that 40.69% of OWPFV faults at the binary level do not match OWPFV faults at the source-code level even if they affect the same locations, since there are several functions parameters and possible replacements for a given location. In order to take into account this aspect, results shown in Figure 3.7 have been updated by reducing the number of Correctly Injected faults for the OWPFV operator and increasing the number of Omitted and Spurious faults by the same amount.

Correctly Injected faults turned out to be 5,927 (Figure 3.7). They represent 47.88% of faults injected by G-SWFIT. The remaining faults injected by G-SWFIT (52.12%) in the binary code do not match to a software fault in the source code, therefore most of G-SWFIT faults are Spurious. Correctly injected faults represent 32.60% of faults injected in the source code, so the remaining faults at the source level (67.40%) are not emulated by G-SWFIT and they result as Omitted faults. The experimental campaign confirms that the accurate injection at the binary level is a challenging task, at least when a complex software system is considered.

The distribution of the causes of inaccuracies (for both Omitted and Spurious faults) are presented in Figure 3.8. These distributions have been obtained by applying the sampling procedure described in Section 3.3.2. Most of spurious faults (Figure 3.8b) are caused by C

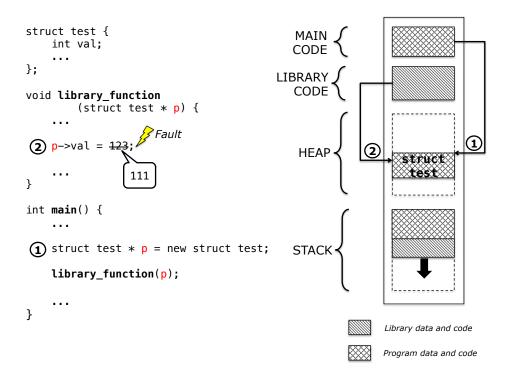

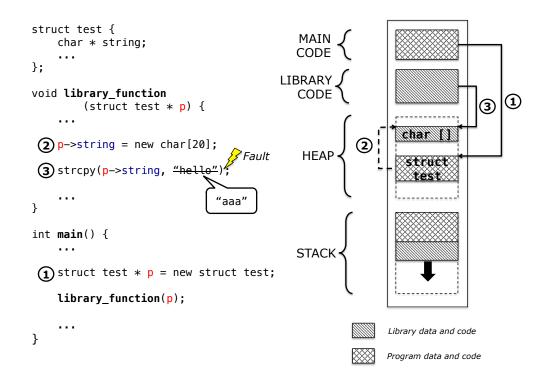

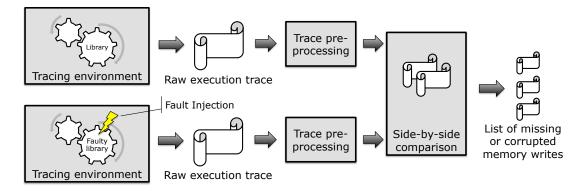

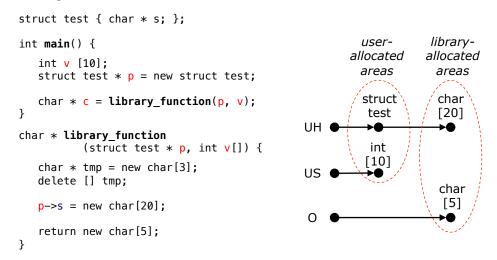

Figure 3.7: Correctly Injected, Spurious, and Omitted Faults